#### **COMP 122**

COMP122

# Computer Org & ASSEMBLY Programming

Rev 8-1-24

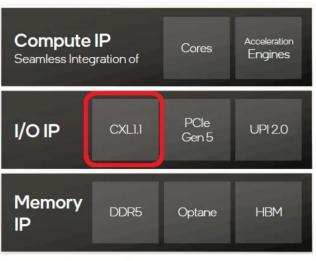

## Intel CPU's

#### Dr Jeff Drobman

website drjeffsoftware.com/classroom.html

email <u>jeffrey.drobman@csun.edu</u>

#### Index

- History

- **❖**i8086 → slide 12

- **♦**i8088 → slide 15

- ❖Intel CPU's → slide 37

- ❖ Future Intel CPU's → slide 98

- ❖Intel GPU's → slide 116

- ❖Intel Strategy → slide 122

- ❖ Fabs/Foundry → slide 127

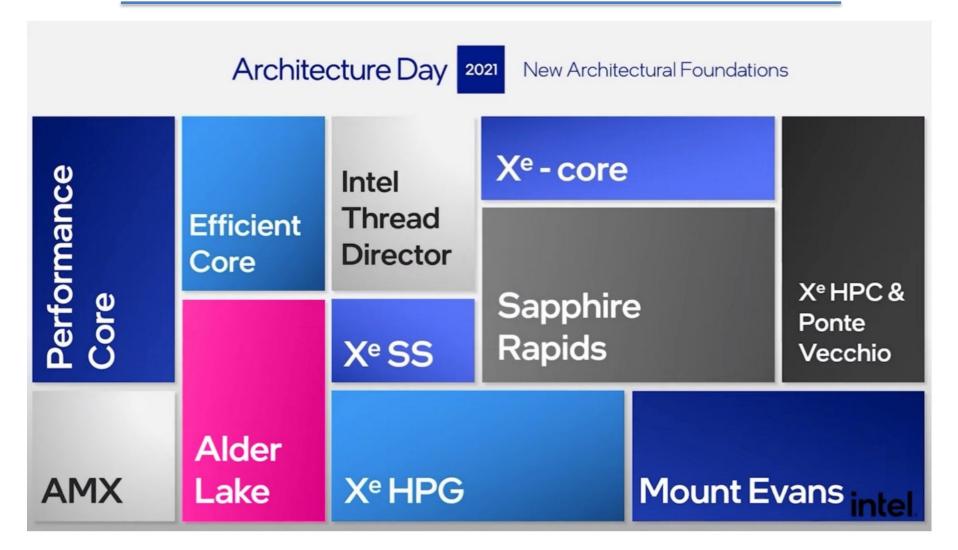

- ❖Intel DevCon 2021 → slide 153

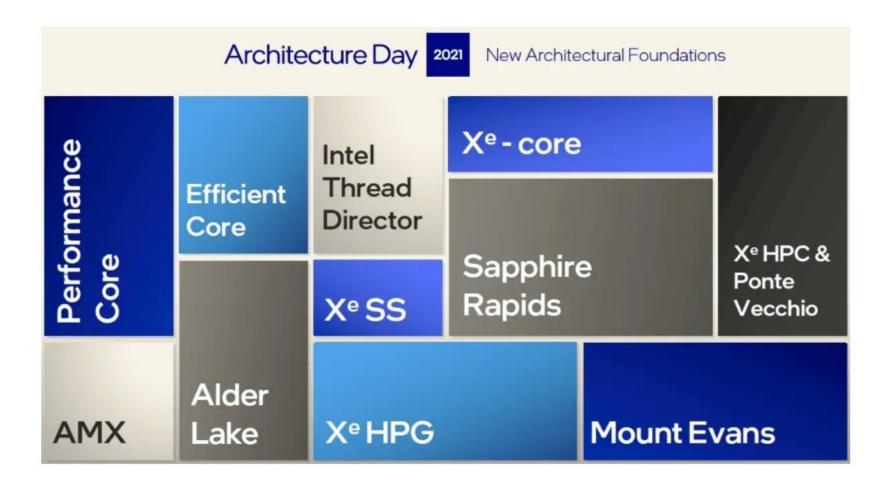

- ❖Intel Arch Day 2021 → slide 189

- ❖Intel News → slide 194

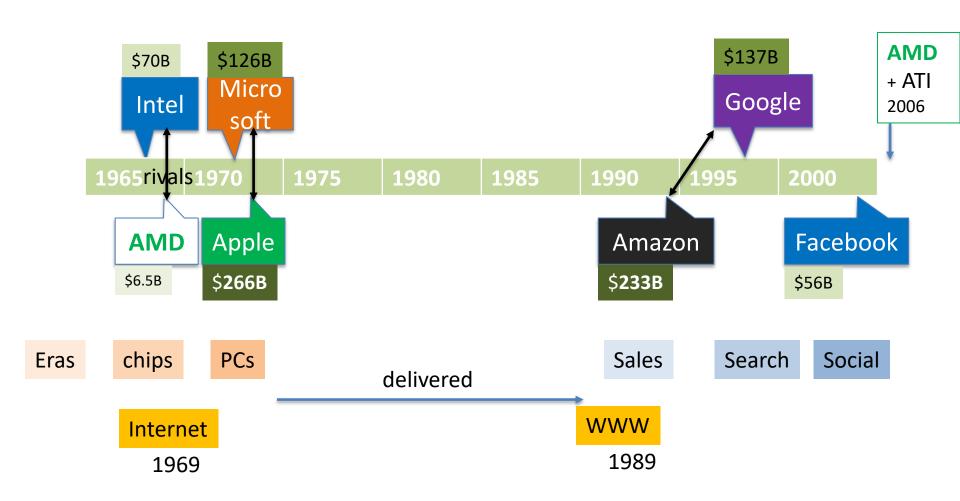

#### Tech Titan Timeline

**Historical Perspective**

#### Intel

\$70B

f. 1968 Tech Titan

2019

Intel's current logo, used since 2006

Intel's headquarters in Santa Clara, California

Founded July 18, 1968; 51 years ago

**Founders**

Gordon Moore

Revenue

Operating

Net income

(intel)

Intel® Xeon® Platinum 9200

Processor

Robert Noyce

US\$70.8 billion (2018)

US\$23.3 billion (2018)

income US\$21.0 billion (2018) 110,200 (2019)[2] Number of employees

> Subsidiaries Mobileye McAfee (49%) Here (15%)

**Products**

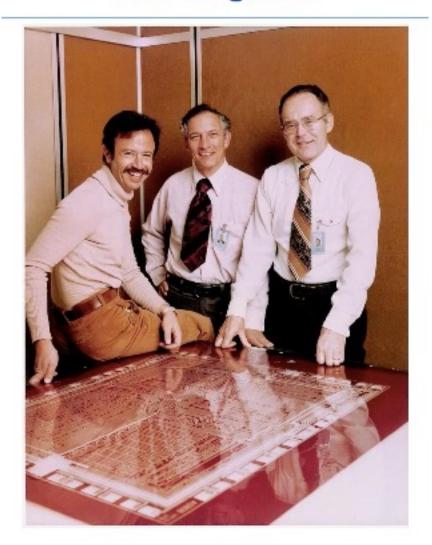

Andy Grove, Robert Noyce 5 and Gordon Moore in 1978

Central processing units Microprocessors Integrated graphics processing units (iGPU) Systems-on-chip (SoCs) Motherboard chipsets Network interface controllers Modems Mobile phones Solid state drives Wi-Fi and Bluetooth Chipsets Flash memory Vehicle automation sensors

Historical market share

In the 1980s Intel was among the top ten sellers of semiconductors (10th in 1987) in the world. In 1992, [13] Intel became the biggest chip maker by revenue and has held the position ever since. Other top semiconductor companies include TSMC, Advanced Micro Devices, Samsung, Texas Instruments, Toshiba and STMicroelectronics.

#### Operating segments [edit]

- Client Computing Group 55% of 2016 revenues produces hardware components used in desktop and notebook computers. [10]

- Data Center Group 29% of 2016 revenues produces hardware components used in server, network, and storage platforms. [10]

- Internet of Things Group 5% of 2016 revenues offers platforms designed for retail, transportation, industrial, buildings and home use. [10]

- Non-Volatile Memory Solutions Group 4% of 2016 revenues manufactures NAND flash memory and 3D XPoint, branded as Optane, products primarily used in solid-state drives.[10]

- Intel Security Group 4% of 2016 revenues produces software, particularly security, and antivirus software.

- Programmable Solutions Group 3% of 2016 revenues manufactures programmable semiconductors (primarily FPGAs). [10]

#### **Bell Labs**

#### Founders HoF

**Wm Shockley**

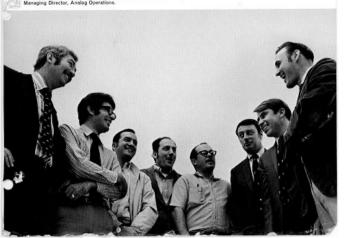

Fairchild Chairman/CEO, LSI Logic founder

CEO, AMD

**Jack Gifford**

AMD cofounder

In 1983, Gifford cofounded Maxim Integrated

**Products**

1969-2002 From left: W. Jerry Sanders III, President and Chairman of the Board. D. John Carey, Managing Director of Complex Digital Operations. Svin E. Simonsen, Director of Engineering, Complex Digital Operations, Frank T. Botte, Director Development, Analog Operations, James R. Giller, Oirector of Engineering, Analog Operations, Eduar J. Turney, Director of Sales and Administration. Josc F. Gifford, Director of Markating and Business Development, R. Lawrence Stonger, Managing Director, Analog Operations.

Fairchild founders (8)

**Bob Noyce**

**Gordon Moore**

Cypress Semi founder

### Intel

1968

#### **Intel Originals**

L to R: Andy Grove Bob Noyce Gordon Moore

Founders:

Bob Noyce

Gordon Moore

### **Intel CEO History**

#### Intel CEOs

| CEO                  | Years     | Background                                                                                                                                |

|----------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Robert N. Noyce      | 1968-1975 | Ph.D. in physics, co-inventor of the IC                                                                                                   |

| Gordan E. Moore      | 1975-1987 | Ph.D. in chemistry, creator of Moore's law                                                                                                |

| Andrew S. Grove      | 1987-1998 | Ph.D. in chemical engineering, wrote Physics and Technology of<br>Semiconductor Devices, co-discoverer of the Deal-Grove<br>Oxidation Law |

| Craig R. Barrett     | 1998-2005 | Ph.D. in materials science, professor at Stamford                                                                                         |

| Paul S. Otellini     | 2005-2013 | MBA                                                                                                                                       |

| Brian M. Krzanich    | 2013-2018 | B.S. chemistry, manufacturing background                                                                                                  |

| Robert H. Swan       | 2018-2021 | MBA                                                                                                                                       |

| Patrick P. Gelsinger | 2021-     | M.S. in electrical engineering, architect of the 80486                                                                                    |

Until 2005 Intel was run by highly technical CEOs.

### Semiconductors & IC's

| r     |      |                                                                                            |

|-------|------|--------------------------------------------------------------------------------------------|

| COM   | P122 | MILESTONES                                                                                 |

|       | 1968 | ❖ Intel founded                                                                            |

|       | 1969 | AMD founded                                                                                |

| MPU   | 1971 | Microprocessor & RAM in MOS invented by Intel (i4004/i8008, i1101/3)                       |

|       | 1972 | Ion Implantation (replaces chemical diffusion) Mfg process                                 |

|       | 1974 | ❖ Digital <b>Watch</b> IC invented                                                         |

|       | 1978 | ❖ Wafer stepper invented for fabs Mfg process                                              |

|       | 1979 | IDT founded (CMOS) Mfg process                                                             |

| ASIC  | 1981 | ❖ LSI Logic founded (ASIC)                                                                 |

| FPGA  | 1984 | Xilinx makes 1 <sup>st</sup> FPGA, MIPS founded as early RISC pioneer (licenses LSI & IDT) |

|       | 1985 | ❖ ARM founded as Acorn RISC Machines                                                       |

| Flash | 1987 | Toshiba intro's Flash EEPROM, TSMC founded (foundry) Mfg process                           |

| GPU   | 1998 | ❖ Nvidia founded (1993) – 1 <sup>st</sup> GPU's (1998)                                     |

|       | 2002 | Intel goes to 300mm (12in) wafers Mfg process                                              |

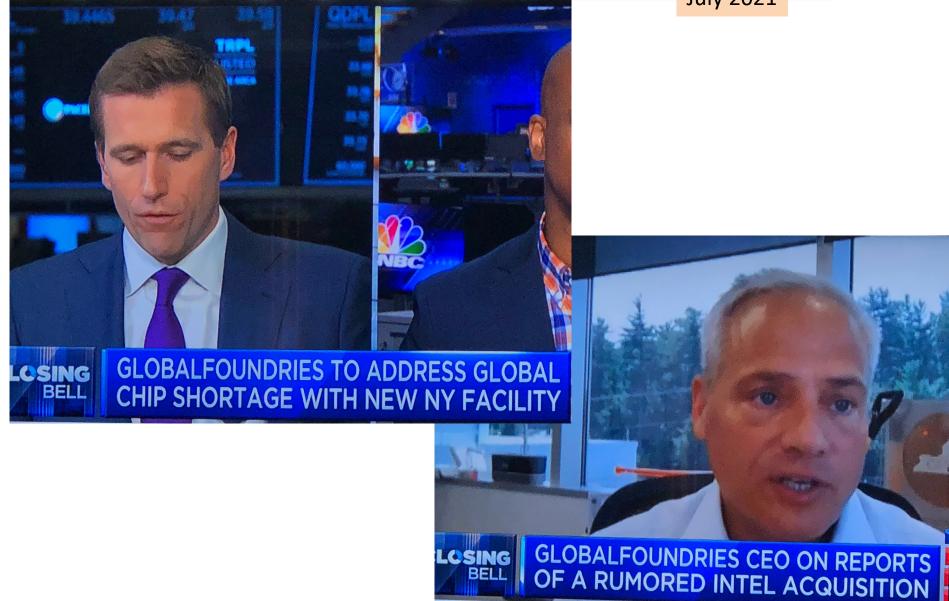

|       | 2009 | AMD spins off fabs to <b>Global Foundries</b> (owner Abu Dhabi) Mfg process                |

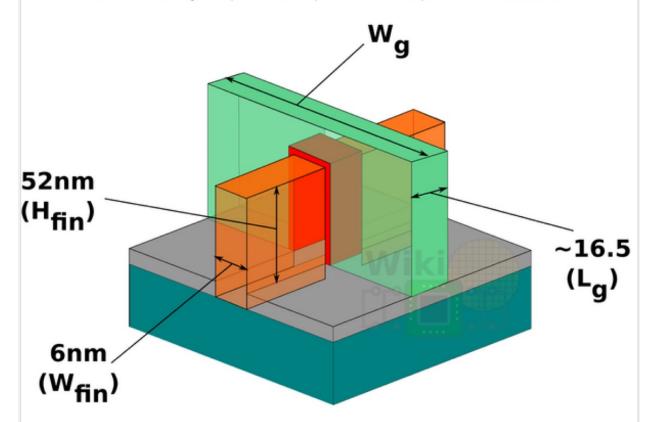

|       | 2011 | ❖ Intel FinFET Mfg process                                                                 |

|       |      |                                                                                            |

| Dec   | 2019 | ❖ Intel intro's 1 <sup>st</sup> QC chip ("Horse Ridge")                                    |

|       | 2020 | ARM intro's "backside power" process  Mfg process                                          |

|       |      |                                                                                            |

#### First MPUs

4004 2300 transistors

8008 3098 transistors

Intel MCS-4 and MCS-8 design team and CPU chips

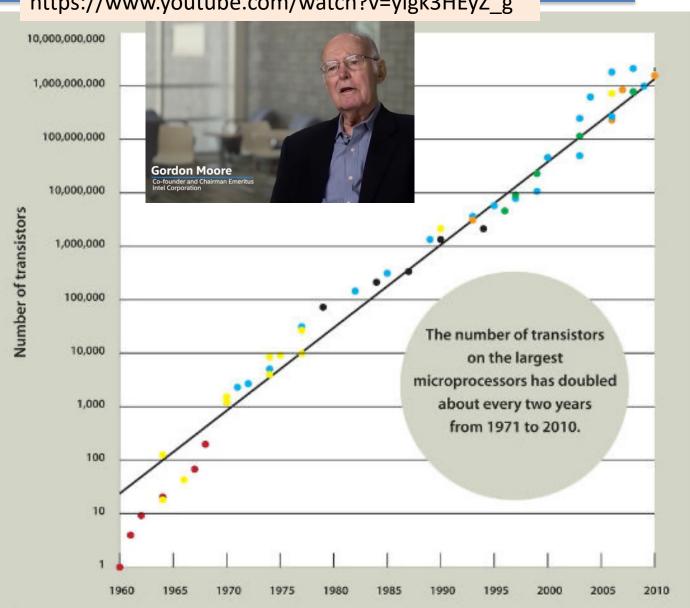

### Chips-Moore's Law

https://www.youtube.com/watch?v=ylgk3HEyZ\_g

# transistors doubles every 2 years

Plaque to Moore\'s Law at the technology plaza in Mountain View, beneath a model of the Silicon crystal

Dave Laws (2018)

### Section

See separate slide set "x86"

#### 8086 Reset Vector

8086 supports 1MB of external memory and reset vector is hardcoded to 0xFFFF0. This gives BIOS 16 bytes at top for JMP to initialization routine somewhere. Well, BIOS was mostly on top of 1MB range, let's say top 64kB or more.

In later versions reset vector was moved to, again top, 0xFFFFFFF0.

Later things changed and today is more complicated cause of microcode updates, security, etc.

In original IBM PC lower 640kB was for RAM, followed by expansion slots and finally BIOS.

#### x86 Modes

COMP122

In the <u>x86-64</u> computer architecture, **long mode** is the mode where a <u>64-bit operating system</u> can access 64-bit <u>instructions</u> and <u>registers</u>. 64-bit programs are run in a sub-mode called 64-bit mode, while 32-bit programs and 16-bit <u>protected mode</u> programs are executed in a sub-mode called compatibility

The results of the mode is the mode where a <u>64-bit operating system</u> can access 64-bit in a sub-mode called for the mode is the mode where a <u>64-bit operating system</u> can access 64-bit in a sub-mode called for the mode is the mode where a <u>64-bit operating system</u> can access 64-bit in a sub-mode called for the mode is the mode in a sub-mode called for the mode is the mode in a sub-mode called for the mode is the mode in a sub-mode called for the mode is the mode in a sub-mode called for the mode is the mode in a sub-mode called for the mode is the mode in a sub-mode called for the mode is the mode in a sub-mode called for the mode is the mode in a sub-mode called for the mode is the mode in a sub-mode called for the mode is the mode in a sub-mode called for the mode is the mode in a sub-mode called for the mode is the mode in a sub-mode called for the mode is the mode in the mode is the mode in the mode in the mode is the mode in the mode is the mode in the mode in the mode is the mode in the mode in the mode is the mode in the mode in the mode is the mode in the mode in the mode is the mode in the mode in the mode in the mode in the mode is the mode in the mode in the mode is the mode in the mode in the mode in the mode in the mode is the mode in the mode

An x86-64 processor acts identically as an <u>IA-32</u> processor when running in real mode or protected mode, which are supported sub-modes when the processor is *not* in long mode.

cannot be natively run in long mode.

"IA" = Intel Architecture

#### Long mode

From Wikipedia, the free encyclopedia

Part of a series on

### Microprocessor modes for the x86 architecture

Real mode (Intel 8086)

8080 emulation mode (NEC V20/V30 only)

Protected mode (Intel 80286)

Unreal mode (Intel 80286)

Virtual 8086 mode (Intel 80386)

System Management Mode (Intel 386SL)

Long mode (AMD Athlon 64)

x86 virtualization (Intel Pentium 4,

AMD Athlon 64)

First supported platform shown in parentheses

### Section

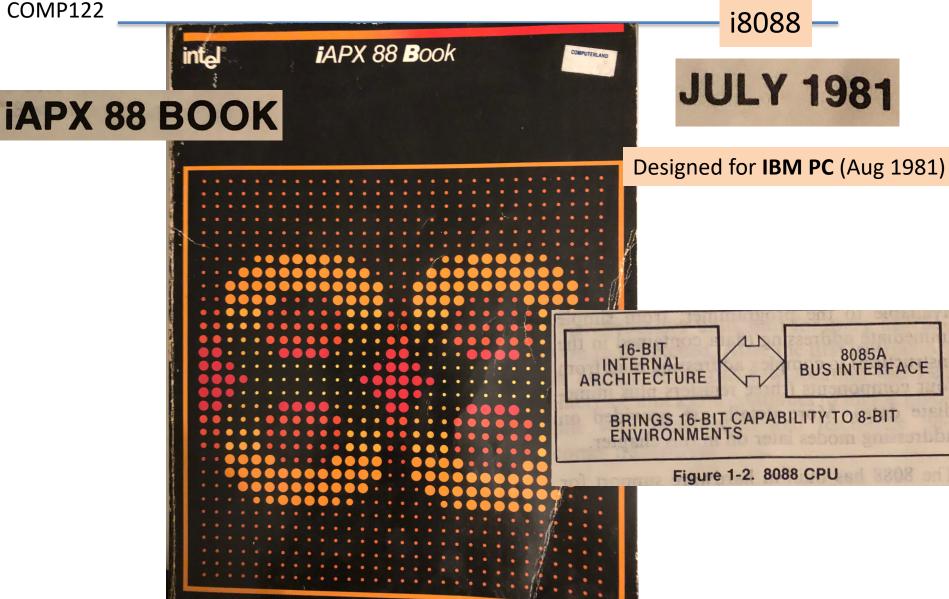

#### Intel i8088

**IBM PC 1981**

Jeff Drobman · just now

Lecturer at California State University, Northridge (2016-present)

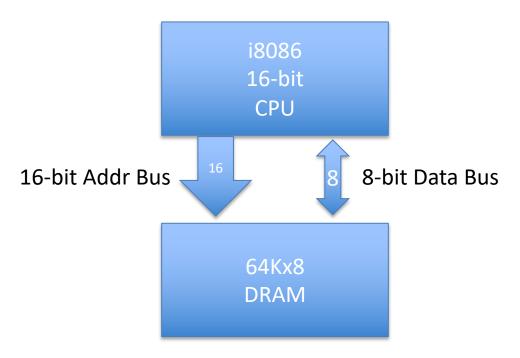

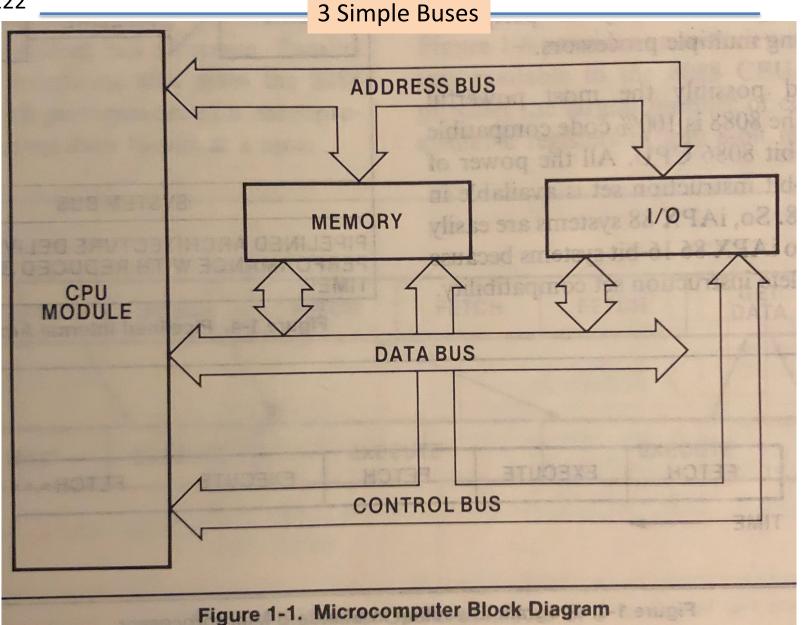

the i8008 and later i8080 were the world's first 8-bit microprocessors. then came the i8086 as the first 16-bit one, followed closely by the M68000 and the Z8000. the i8088 was a special design for IBM's PC: an i8086 with an 8-bit data bus (so IBM only had to build an 8-bit memory, but it was 16-bit addressable (64KiB).

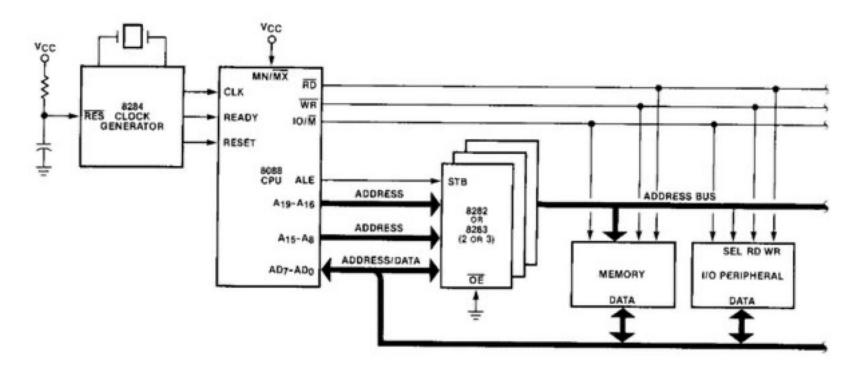

#### i8088 Muxed Buses

COMP122 Quora

Joe Zbiciak · Follow

Processor and memory system architect for ~25 years ·

The 8086 and 8088 do not require a data bus transceiver.

Figure 4-11. Minimum Mode 8088 Demultiplexed Address Bus

### Old Intel 8088 Registers

| on sed  | AH      | AL Figure | Baokus<br>Bakhir | AX |

|---------|---------|-----------|------------------|----|

| dolo    | BH      | ENINIBI   | 1919 30          | BX |

| ord 880 | CH g    | indiaci   | s for the        | CX |

| the 80  | SO HOES | annoli.   | d exed           | DX |

|         |         | Data Grou |                  | Y  |

## Old Intel 8088 Registers

|           |                             | 18088                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                 |

|-----------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 42 Tables | DATAREC                     | SISTERS TO THE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | the string manipulations, th    |

| 12 4707   | 78 nonsentent wellto        | C) soldanb r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | HAG, which combleo o            |

| AX        | AH                          | AL MAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | il interrupting and the TI      |

| вх        | ВН                          | BL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | puls the processor into a       |

| СХ        | CH PROPERTY                 | CL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Rudandap theraord to            |

| DX        | nesses at DH trackmass      | ST DL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | oc detailed (dispussion or      |

| d sture   | licates the sign of the     | Mi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | To Byman mailing and 12         |

|           | POINTER AND IN              | DEX REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | f (the equilibry carry flag) is |

| 128 33    | 15 PF (the parity flatt     | (S amy many                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | STACK POINTER                   |

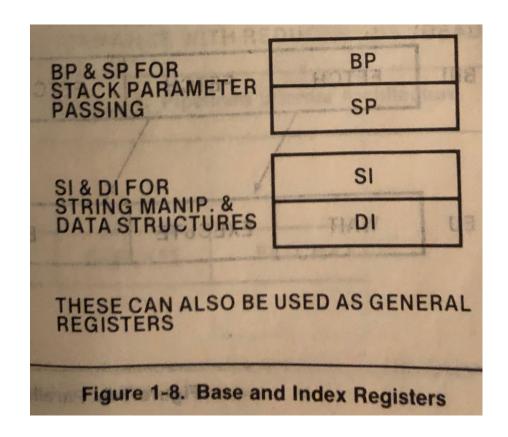

| SP        | n panty, an even nu         | SVS CONTRACTOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DOPPOWIED WITH AND SINK WILL    |

| BP        | Section of Design of the S  | COLUMN TO THE PARTY OF THE PART | BASE POINTER                    |

| SI        | To the factor of the second | Townson                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SOURCE INDEX                    |

| DI        | Dainons                     | eno promotion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DESTINATION INDEX               |

|           |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10 2 2 Land 10 10 1             |

### Old Intel 8088 Registers

EA

#### FIRST OPERAND CHOICE DEPENDS ON ADDRESSING MODE:

| FIRST OPERAND IN MEMORY                                                    |                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | FIRST OPERAND IN REGISTER                            |                                              |                                              |

|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------|----------------------------------------------|

|                                                                            |                                                                                                                                                                 | DIRECT ADDRESSING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | MOD = 11                                             |                                              |                                              |

| MOD = 01 : DISP = DISP-LO SIGN<br>EXTENDED<br>10 : DISP = DISP-HI, DISP-LO |                                                                                                                                                                 | MOD = 00<br>AND<br>R/M = 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                      |                                              |                                              |

|                                                                            |                                                                                                                                                                 | A STATE OF THE STA |                                                      | REGISTER                                     |                                              |

|                                                                            |                                                                                                                                                                 | OPERAND EFFECTIVE<br>ADDRESS =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/M:                                                 | 8-BIT                                        | 16-BIT                                       |

|                                                                            | OPERAND<br>EFFECTIVE ADDRESS                                                                                                                                    | DISP-HI, DISP-LO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | mage own                                             | (W=0)                                        | (W = 1)                                      |

| R/M:<br>000<br>001<br>010<br>011<br>100<br>101<br>110<br>111               | (BX) + (SI) + DISP<br>(BX) + (DI) + DISP<br>(BP) + (SI) + DISP<br>(BP) + (DI) + DISP<br>(SI) + DISP<br>(DI) + DISP<br>(BP) + DISP<br>(BP) + DISP<br>(BX) + DISP | These opers through count count form through count form through count for the count fo | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | AL<br>CL<br>DL<br>BL<br>AH<br>CH<br>DH<br>BH | AX<br>CX<br>DX<br>BX<br>SP<br>BP<br>SI<br>DI |

Where ( ) means "contents of"

Figure 2-5. Determining First Operand

<sup>\*</sup>Exception—direct addressing mode

EA

|                   | DATA         | STACK                                |                                      |

|-------------------|--------------|--------------------------------------|--------------------------------------|

| DATA<br>STRUCTURE | WITHOUT BASE | WITH BASE                            | more care in annual con-             |

| SIMPLE _          | DIRECT       | BX + OFFSET                          | BP + OFFSET                          |

| VARIABLE          |              | BX + SI                              | BP + SI                              |

| ARRAYS            | SI           | BX + DI                              | BP + DI                              |

| ARRAYS            | SI + OFFSET  | BX + SI + OFFSET<br>BX + DI + OFFSET | BP + SI + OFFSET<br>BP + DI + OFFSET |

| OF RECORDS        | DI + OFFSET  | BX + DI + OTTOET                     | tack has somboome svi                |

Figure 2-6. Effective Addresses Used with Different Data Structures

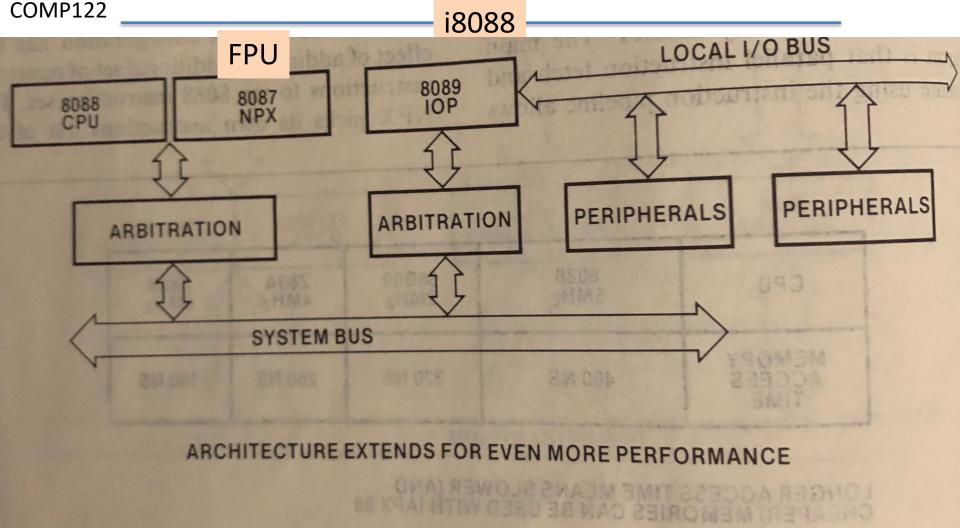

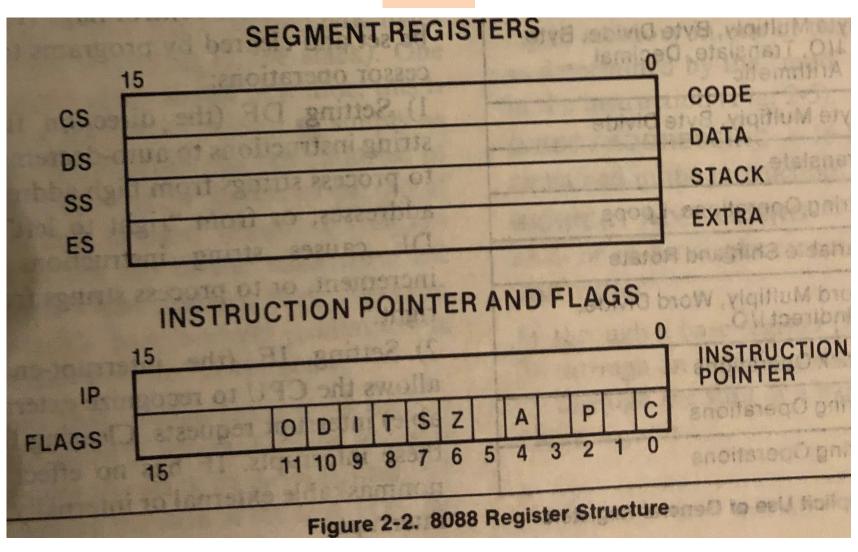

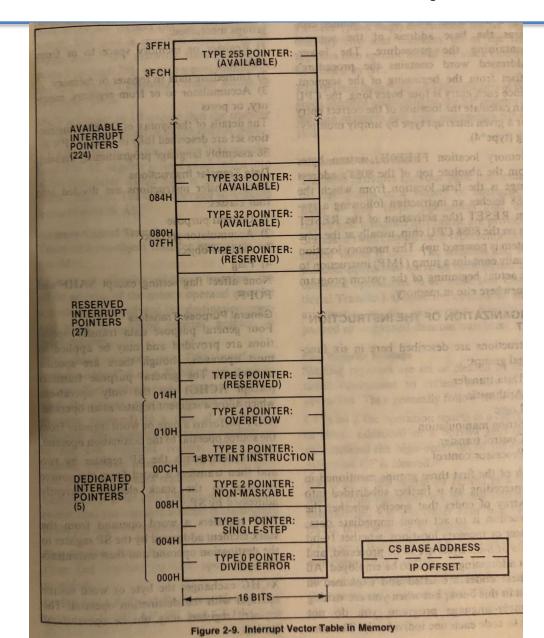

i8088

### "reg" Field Bit Assignments:

| 16-Bit (w = 1)                                                               | 8-Bit $(w = 0)$                                                              | Segment                          |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------|

| 000 AX<br>001 CX<br>010 DX<br>011 BX<br>100 SP<br>101 BP<br>110 SI<br>111 DI | 000 AL<br>001 CL<br>010 DL<br>011 BL<br>100 AH<br>101 CH<br>110 DH<br>111 BH | 00 ES<br>01 CS<br>10 SS<br>11 DS |

i8088

### "r/m" Field Bit Assignments:

| r/m | Operand Address    |

|-----|--------------------|

| 000 | (BX) + (SI) + DISP |

| 001 | (BX) + (DI) + DISP |

| 010 | (BP) + (SI) + DISP |

| 011 | (BP) + (DI) + DISP |

| 100 | (SI) + DISP        |

| 101 | (DI) + DISP        |

| 110 | (BP) + DISP        |

| 111 | (BX) + DISP        |

DISP = Offset

EA

DISP follows 2nd byte of instruction (before data if required).

\*except if mod = 00 and r/m = 110 then EA = disp-high: disp-low

i8088

#### **Encoding:**

## Memory or Register Operand with Register Operand:

000000dw mod reg r/m

2 bytes

if d = 1 then LSRC = REG, RSRC = EA, DEST = REG else LSRC = EA, RSRC = REG, DEST = EA

#### Immediate Operand to Memory or Register Operand:

100000sw mod000r/m

data

data if s:w=01

4 bytes

scription:

LSRC = EA, RSRC = data, DEST = EA bas 72, 39, 30, 10, 3A casabagu GGA

#### Immediate Operand to Accumulator:

0000010w

data

data if w=1

3 bytes

if w = 0 then LSRC = AL, RSRC = data, DEST = AL else LSRC = AX, RSRC = data, DEST = AX

### Old Intel 8088 Clocks

EA

| EA COMPONENTS OF                      | CLOCKS*       |

|---------------------------------------|---------------|

| Displacement Only muzze eldass        | alwaya repe   |

| Base or Index Only (BX,BP,SI,DI)      | 219 5         |

| Displacement di sum anoiburita        |               |

| Base or Index (BX,BP,SI,DI)           | Edus System   |

| Base BP+DI, BX+SI                     | MISH SISCA    |

| Index BP+SI, BX+DI                    | this section. |

| Displacement BP+DI+DISP<br>BX+SI+DISP | sho milita of |

| Base BP+SI+DISP                       | 12            |

| Index BX+DI+DISP                      | issemeny La   |

<sup>\*</sup> Add 2 clocks for segment override

Figure 2-10. Effective Address Calculation Time

# Old Intel 8088 Clocks/Bytes

i8088

| ADD Operands                                                                                                                     | Clocks*                                            | Transfers        | Bytes                         | ADD Coding Examples                                                            |

|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------|-------------------------------|--------------------------------------------------------------------------------|

| register, register<br>register, memory<br>memory, register<br>register, immediate<br>memory, immediate<br>accumulator, immediate | 3<br>9(13) + EA<br>16(24) + EA<br>4<br>17(25) + EA | -<br>1<br>2<br>- | 2<br>2-4<br>2-4<br>3-4<br>3-6 | ADD CX, DX ADD DI. [BX]. ALPHA ADD TEMP, CL ADD CL. 2 ADD ALPHA, 2 ADD AX, 200 |

\*b(w): where b denotes the number of clock avalage

Memory (vars)

| gned bin | ary, signed binary integration |  |  |

|----------|--------------------------------|--|--|

|          | GENERAL PURPOSE                |  |  |

| MOV      | Move byte or word              |  |  |

| PUSH     | Push word onto stack           |  |  |

| POP      | Pop word off stack             |  |  |

| XCHG     | Exchange byte or word          |  |  |

| XLAT     | Translate byte                 |  |  |

|          | INPUT/OUTPUT                   |  |  |

| IN       | Input byte or word             |  |  |

| OUT      | Output byte or word            |  |  |

|          | ADDRESS OBJECT                 |  |  |

| LEA      | Load effective address         |  |  |

| LDS      | Load pointer using DS          |  |  |

| LES      | Load pointer using ES          |  |  |

|          | FLAG TRANSFER                  |  |  |

| LAHF     | Load AH register from flags    |  |  |

| SAHF     | Store AH register in flags     |  |  |

| PUSHF    | Push flags onto stack          |  |  |

| POPF     | Pop flags off stack            |  |  |

| Tallia Bar | ADDITION                          |  |  |  |

|------------|-----------------------------------|--|--|--|

| ADD        | Add byte or word                  |  |  |  |

| ADC        | Add byte or word with carry       |  |  |  |

| INC        | Increment byte or word by 1       |  |  |  |

| AAA        | ASCII adjust for addition         |  |  |  |

| DAA        | Decimal adjust for addition       |  |  |  |

| -0200033   | SUBTRACTION                       |  |  |  |

| SUB        | Subtract byte or word             |  |  |  |

| SBB        | Subtract byte or word with borrow |  |  |  |

| DEC        | Decrement byte or word by 1       |  |  |  |

| NEG        | Negate byte or word               |  |  |  |

| CMP        | Compare byte or word              |  |  |  |

| AAS        | ASCII adjust for subtraction      |  |  |  |

| DAS        | Decimal adjust for subtraction    |  |  |  |

|            | MULTIPLICATION                    |  |  |  |

| MUL        | Multiply byte or word unsigned    |  |  |  |

| IMUL       | Integer multiply byte or word     |  |  |  |

| AAM        | ASCII adjust for multiply         |  |  |  |

| 3610 /4 10 | DIVISION                          |  |  |  |

| DIV        | Divide byte or word unsigned      |  |  |  |

| IDIV       | Integer divide byte or word       |  |  |  |

| AAD        | ASCII adjust for division         |  |  |  |

| CBW        | Convert byte to word              |  |  |  |

| CWD        | Convert word to doubleword        |  |  |  |

Figure 1-16. Data Transfer Instructions

Figure 1-17. Arithmetic Instructions

| LOGICALS |                                            |  |  |  |  |

|----------|--------------------------------------------|--|--|--|--|

| NOT      | "Not" byte or word                         |  |  |  |  |

| AND      | "And" byte or word                         |  |  |  |  |

| OR       | "Inclusive or" byte or word                |  |  |  |  |

| XOR      | "Exclusive or" byte or word                |  |  |  |  |

| TEST     | "Test" byte or word                        |  |  |  |  |

| SHIFTS   |                                            |  |  |  |  |

| SHL/SAL  | Shift logical/arithmetic left byte or word |  |  |  |  |

| SHR      | Shift logical right byte or word           |  |  |  |  |

| SAR      | Shift arithmetic right byte or word        |  |  |  |  |

| ROTATES  |                                            |  |  |  |  |

| ROL      | Rotate left byte or word                   |  |  |  |  |

| ROR      | Rotate right byte or word                  |  |  |  |  |

| RCL      | Rotate through carry left byte or word     |  |  |  |  |

| RCR      | Rotate through carry right byte or word    |  |  |  |  |

| Figure 1-18. Bit Manipulation Instruct |

|----------------------------------------|

|----------------------------------------|

| MOVS        | Move byte or word string        |  |  |

|-------------|---------------------------------|--|--|

| MOVSB/MOVSW | Move byte or word string        |  |  |

| CMPS        | Compare byte or word string     |  |  |

| SCAS        | Scan byte or word string        |  |  |

| LODS        | Load byte or word string        |  |  |

| STOS        | Store byte or word string       |  |  |

| REP         | Repeat                          |  |  |

| REPE/REPZ   | Repeat while equal/zero         |  |  |

| REPNE/REPNZ | Repeat while not equal/not zero |  |  |

Figure 1-19. String Instructions

|         | THE PROPERTY OF THE PARTY OF TH | UNCONDITIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NAL TRANSFERS              |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|