#### **COMP 122**

Fall 2023

Rev7-13-23

#### **ASSEMBLY Programming**

## **Logic Design**

Dr Jeff Drobman

website drjeffsoftware.com/classroom.html

email <u>jeffrey.drobman@csun.edu</u>

#### Index

- $\Leftrightarrow$  Logic  $\Rightarrow$  slide 3

- ❖ Transistors to Gates → slide 13

- ❖ Arithmetic → slide 19

- ❖ AMD Catalog of Analog (Linear) → slide 31

- ❖ Digtial MSI: ALU → slide 35

- ❖ Digtial MSI: PIC, Mux/Dec → slide 40

- ❖ Logic Minimize → slide 54

- ❖ Memory (RAM) → slide 62

- ❖ Sequential Logic → slide 67

- ❖ Logic: Multi/Div → slide 78

- ❖ Logic Timing (AC) → slide 97

- ❖ State Machines (FSM) → slide 103

- ❖ Computer Logic Boards → slide 105

#### Section

#### Logic

```

Relational Operators

less than

less than or equal to

greater than

greater than or equal to

equal to

!= not equal

```

any type → boolean

if  $(x \le y+3) \& x > 2 \mid | FLAG == true$

```

_FLAG == true \Leftrightarrow _FLAG

FLAG == false \Leftrightarrow ! FLAG

```

```

&& short circuit AND

|| short circuit OR

! NOT

A exclusive OR

```

boolean → boolean

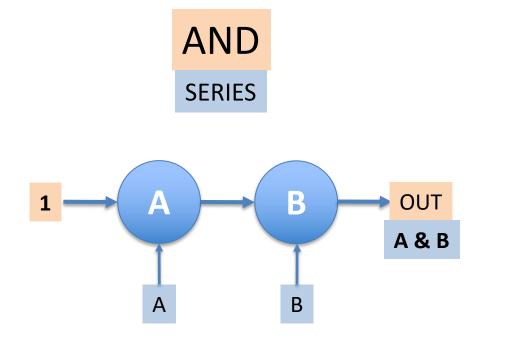

- ❖ AND has 2 uses:

- 1) Mask (1 lets in)

- 2) Filter (0 keeps out)

- ❖ XOR has 2 uses:

- 1) Bit complement/toggle

- 2) Bit equal

#### Logic Book

COMP122

allaboutcircuits.com

## Chapters in this Volume

Ch. 1 - Numeration Systems

Ch. 2 - Binary Arithmetic

Ch. 3 - Logic Gates

Ch. 4 - Switches

Ch. 5 - Electromechanical Relays

Ch. 6 - Ladder Logic

Ch. 7 - Boolean Algebra

Ch. 8 - Karnaugh Mapping

> K-maps

Ch. 9 - Combinational Logic Functions

Ch. 10 - Multivibrators

Ch. 11 - Sequential Circuits

Ch. 12 - Shift Registers

Ch. 13 - Digital-Analog Conversion

Ch. 14 - Digital Communication

Ch. 15 - Digital Storage (Memory)

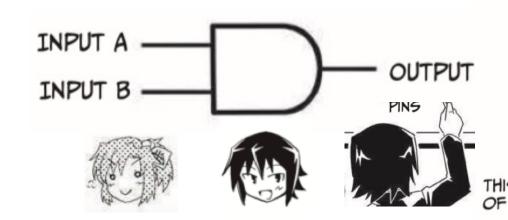

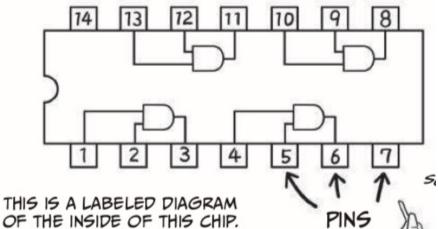

#### Logic Comic Book

COMP122

Manga Guide

https://nostarch.com/download/MangaGuidetoMicroprocessors\_sample\_Chapter2.pdf

#### **Truth Tables**

COMP122

| OR |   |        |  |   | AND |        |

|----|---|--------|--|---|-----|--------|

| X  | Υ | X    Y |  | X | Y   | X && Y |

| 0  | 0 | 0      |  | 0 | 0   | 0      |

| 0  | 1 | 1      |  | 0 | 1   | 0      |

| 1  | 0 | 1      |  | 1 | 0   | 0      |

| 1  | 1 | 1      |  | 1 | 1   | 1      |

#### XOR

|      | Χ       | V    | χлγ |   |

|------|---------|------|-----|---|

|      | ^       | Y    | V I |   |

| pass | 0       | 0    | 0   |   |

|      | 0       | 1    | 1   |   |

| flip | 1       | 0    | 1   |   |

| ıııp | 1       | 1    | 0   | K |

|      | 1       | 1    |     |   |

|      | control | data |     |   |

#### **INclusive**

- ❖ AND has 2 uses:

- 1) Mask (1 lets in)

- 2) Filter (0 keeps out)

- ❖ XOR has 2 uses:

- 1) Bit complement/toggle

- 2) Bit equal

**EXclusive**

### **Bit-wise Operations**

Appendix G

p. 751

NEW

| Operator | Name                          | Example                     | Result                 |                 |

|----------|-------------------------------|-----------------------------|------------------------|-----------------|

| &        | Bitwise AND                   | 11101 & 00111               | 00101                  |                 |

| Ī        | Bitwise OR                    | 00010   11000               | <b>1101</b> 0          |                 |

| ۸        | Bitwise XOR                   | 00111 ^ 11111               | 11000                  | bit flip        |

| ~        | 1's complement                | 00111100                    | 11000011               |                 |

| <<       | Left shift (*2 <sup>n</sup> ) | <b>10</b> 101010 << 2       | 10101000               | *2 <sup>n</sup> |

| >>       | Right shift, arith SE         | 101010 <mark>11</mark> >> 2 | <b>111</b> 01010       |                 |

| >>>      | Right shift, logical          | 101010 <mark>11</mark> >> 2 | <mark>001</mark> 01010 |                 |

Integer types only

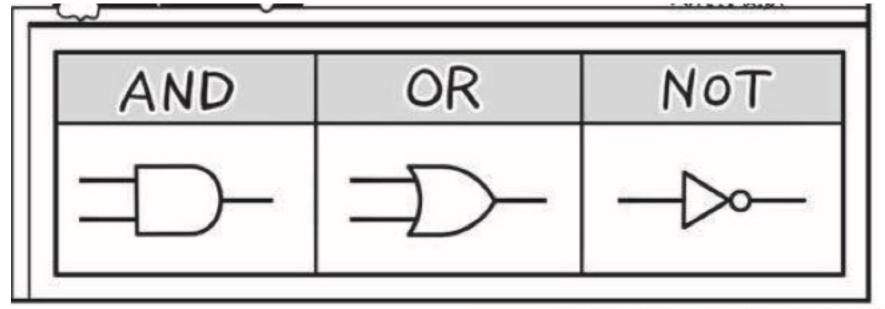

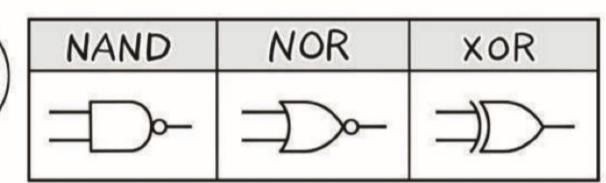

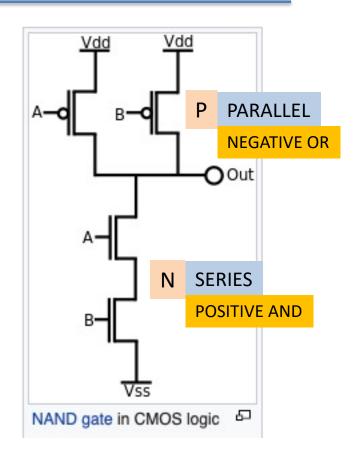

#### **Compound Logic Gates**

Manga Guide

OTHER BASIC GATES (NAND, NOR, AND XOR)

OKAY, LET'S TAKE A LOOK AT NAND, NOR, AND XOR\* GATES NEXT.

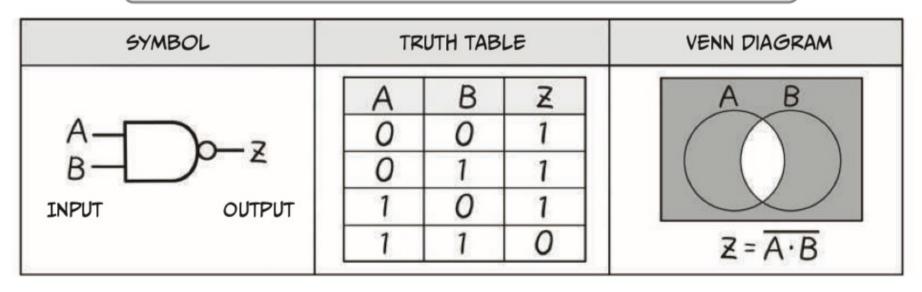

#### Compound Logic: NAND

Manga Guide

NAND GATE (LOGIC INTERSECTION COMPLEMENT GATE)

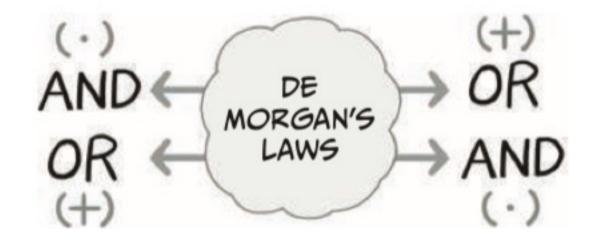

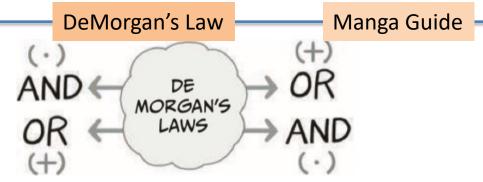

#### Logic Gates: Polarity

DeMorgan's Law

Manga Guide

$$\overline{A \cdot B} = \overline{A} + \overline{B}$$

$$\overline{A+B} = \overline{A} \cdot \overline{B}$$

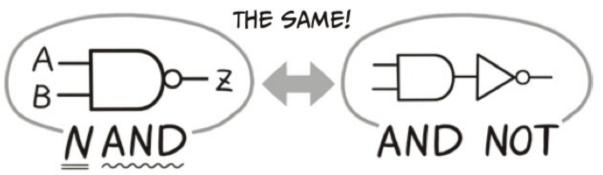

#### Logic Gates: Polarity

That's it! It also means that we can use De Morgan's laws to show our circuits in different ways. Using this technique, it's easy to simplify schematics when necessary.

BOTH OF THESE ARE NAND GATES!

BOTH OF THESE ARE NOR GATES!

#### Section

# Transistors Make Gates

#### **Transistors to Computers**

Quora-

## If computers are really just many (billions) of on/off switches, how do they perform operations?

**Jeff Drobman**, Lecturer at California State University, Northridge (2016-present)

Answered just now

via a multi-level hierarchy of digital logic. transistors are combined to form logic "gates" of simple logic functions (AND, OR, NOT). the gates are combined to form more complex functions such as decoders, ALUs, and multiplexers. these functional blocks are then combined further into ever more complex logic blocks such as EU's and then CPU cores. also, random logic implements the ICU as an FSM which includes pipelining. besides logic, computers have "storage" in the form of registers and memory (at up to 4 levels) via DRAM and SRAM cells formed from transistors (and a capacitor).

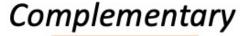

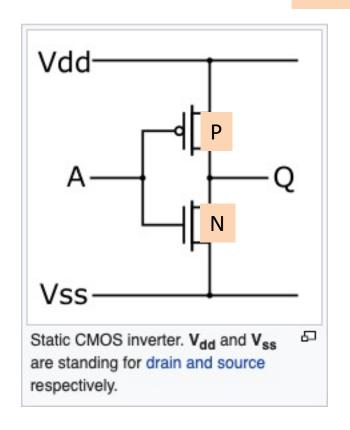

#### $P \rightarrow N \rightarrow C MOS$

Device/Xtor

Physical

Level

**Inverter/Gates**

CMOS INVERTER

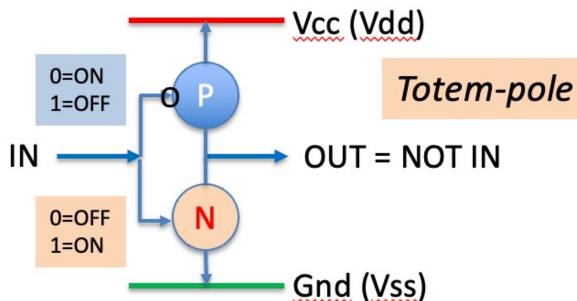

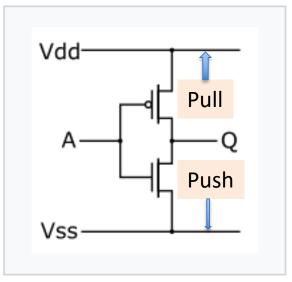

#### **MOS** Gates

**MOSFET**

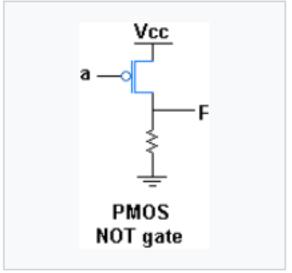

NMOS inverter

PMOS inverter

Static CMOS inverter

NOT

**CMOS**

P/N Totem pole

Push-Pull

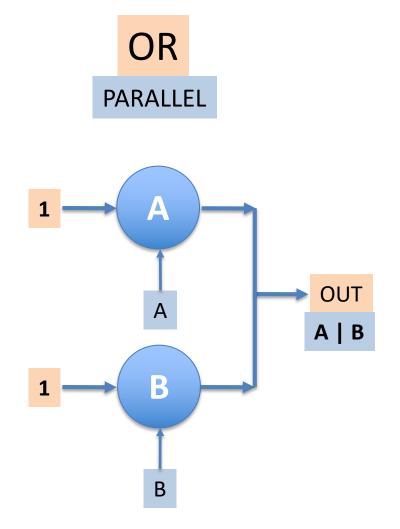

#### Logic Gates: AND, OR

#### **CMOS** Gates

COMP122

#### **MOSFET**

#### Section

## Arithmetic

## ALU Ops MARS

| add \$t1,\$t2,\$t3   | Addition with overflow : set \$t1 to (\$t2 plus \$t3)                               |

|----------------------|-------------------------------------------------------------------------------------|

| add.d \$f2,\$f4,\$f6 | Floating point addition double precision : Set \$f2 to double-precision floating p  |

| add.s \$f0,\$f1,\$f3 | Floating point addition single precision : Set \$f0 to single-precision floating p  |

| addi \$t1,\$t2,-100  | Addition immediate with overflow : set \$t1 to (\$t2 plus signed 16-bit immediate)  |

| addiu \$t1,\$t2,-100 | Addition immediate unsigned without overflow: set \$t1 to (\$t2 plus signed 16-bit  |

| addu \$t1,\$t2,\$t3  | Addition unsigned without overflow: set \$t1 to (\$t2 plus \$t3), no overflow       |

| and \$t1,\$t2,\$t3   | Bitwise AND : Set \$t1 to bitwise AND of \$t2 and \$t3                              |

| andi \$t1,\$t2,100   | Bitwise AND immediate : Set \$t1 to bitwise AND of \$t2 and zero-extended 16-bit im |

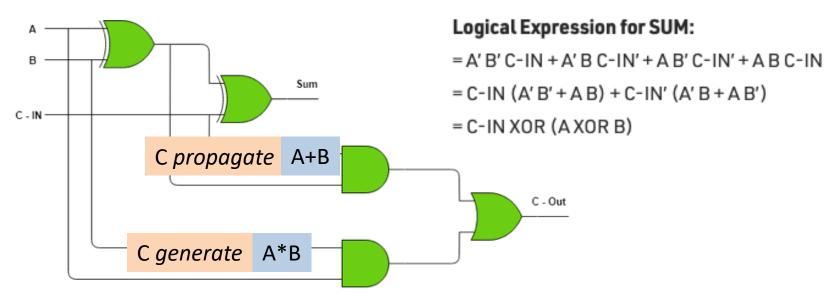

#### Full Adder in Digital Logic <del>26</del> GeeksforGeeks —

|   | Inputs |      | Out | tputs   |

|---|--------|------|-----|---------|

| A | В      | C-IN | Sum | C - Out |

| 0 | 0      | 0    | 0   | 0       |

| 0 | 0      | 1    | 1   | 0       |

| 0 | 1      | 0    | 1   | 0       |

| 0 | 1      | 1    | 0   | 1       |

| 1 | 0      | 0    | 1   | 0       |

| 1 | 0      | 1    | 0   | 1       |

| 1 | 1      | 0    | 0   | 1       |

| 1 | 1      | 1    | 1   | 1       |

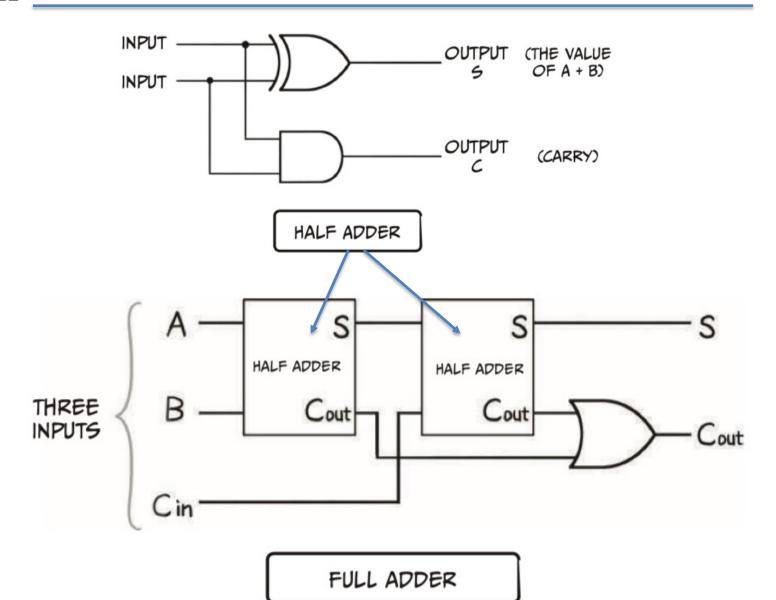

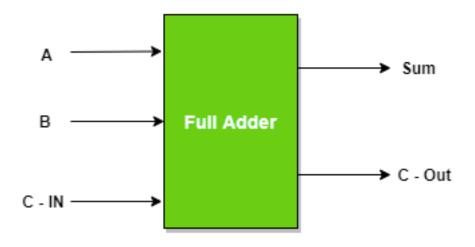

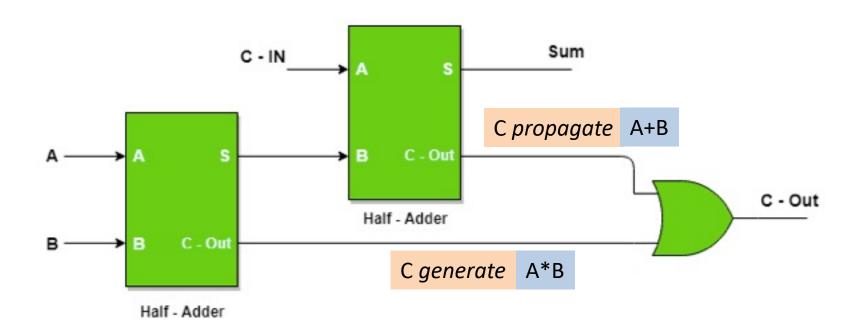

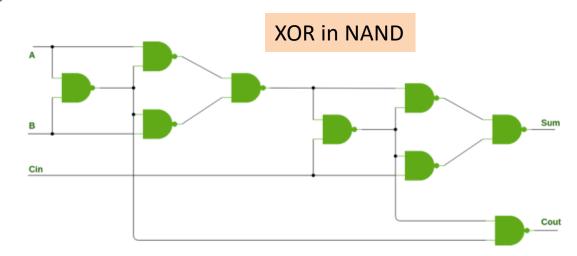

#### Implementation of Full Adder using Half Adders

2 Half Adders and a OR gate is required to implement a Full Adder.

COMP122

Therefore COUT = AB + C-IN (A EX - OR B)

#### Full Adder logic

#### Implementation of Full Adder using NAND gates:

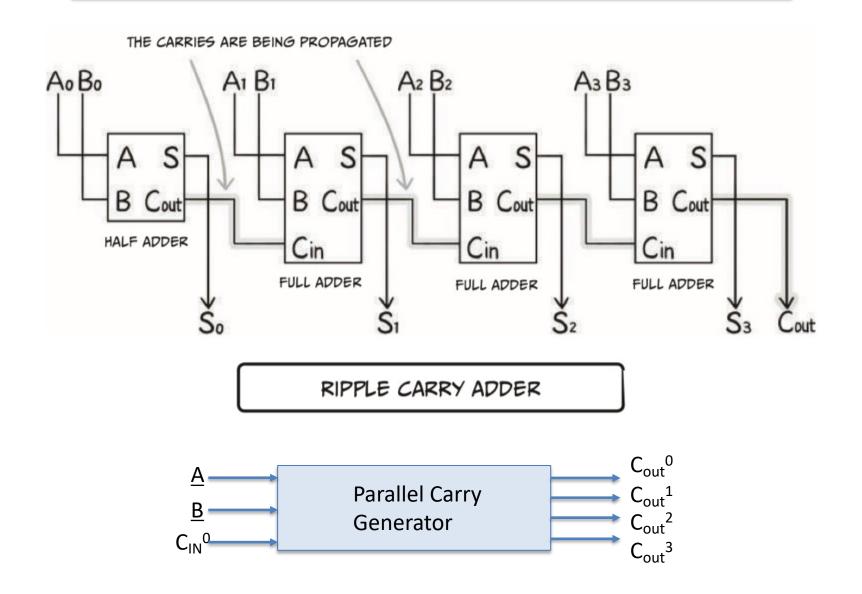

### Adders: Ripple Carry

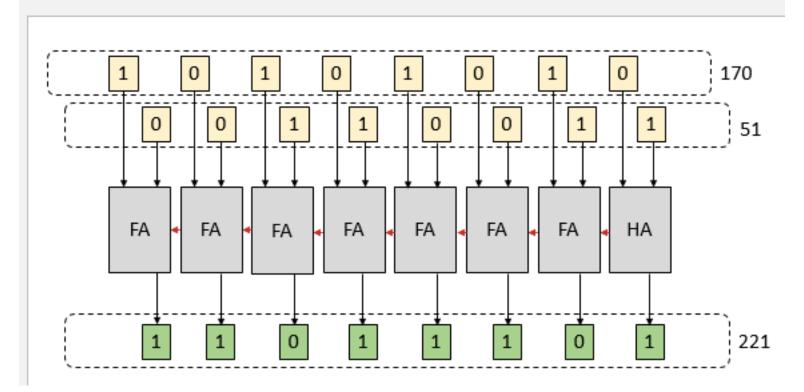

#### The 8-Bit Adder Principle

The 8-bit adder adds the numbers digit by digit, as can be seen in the schematic diagram below. In this example, the integers 170 and 51 represent input a and b, respectively, and the resulting output is the sur 221. The first adder does not have any carry-in, and so it is represented by a half adder (HA) instead of a full adder (FA).

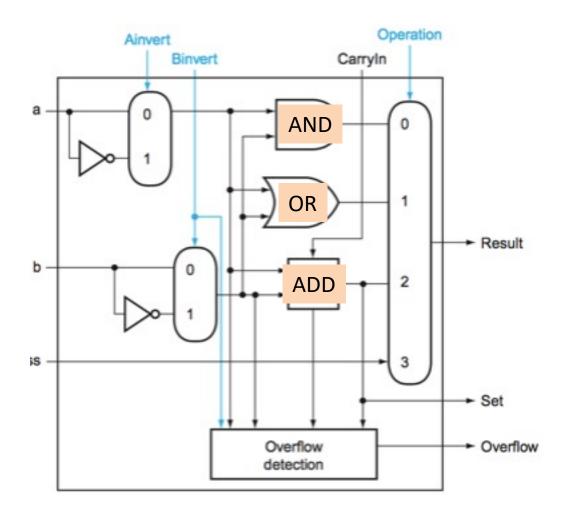

## MIPS/MARS ALU

#### MIPS ALU in Verilog

HDL

Figure 8.5.15: A Verilog behavioral definition of a MIPS ALU (COD Figure B.5.15).

```

module MIPSALU (ALUctl, A, B, ALUOut, Zero);

input [3:0] ALUctl;

input [31:0] A.B;

output reg [31:0] ALUOut;

output Zero;

assign Zero = (ALUOut==0); //Zero is true if ALUOut is 0

always @(ALUctl, A, B) begin //reevaluate if these change

case (ALUctl)

0: ALUOut <= A & B:

1: ALUOut <= A | B;

2: ALUOut <= A + B:

6: ALUOut <= A - B:

7: ALUOut <= A < B ? 1 : 0;

12: ALUOut \leftarrow \sim (A | B); // result is nor

default: ALUOut <= 0;

endcase

end

endmodule

```

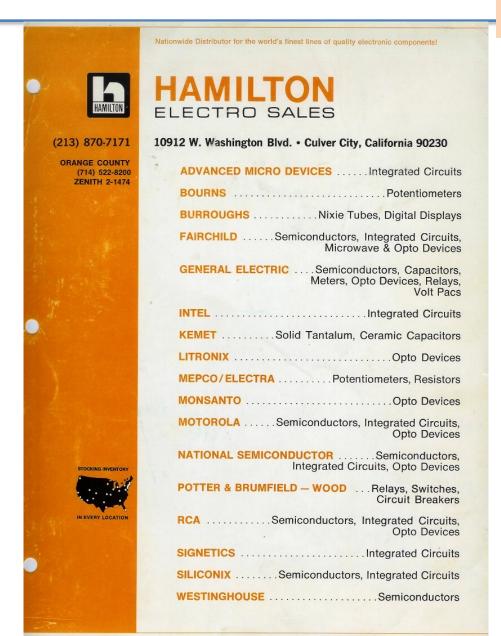

#### Section

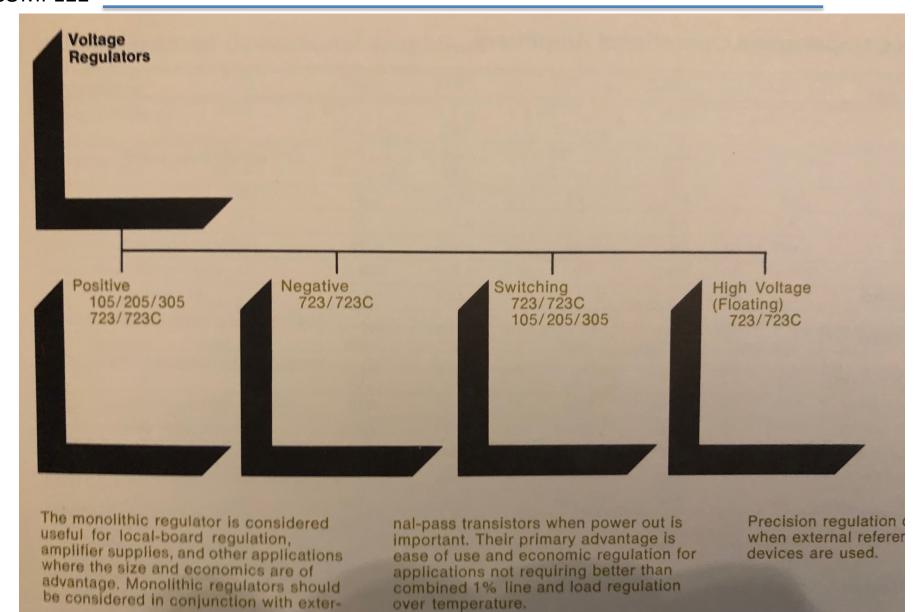

## AMD Products (1971)

- Analog

- Op Amps

- Voltage Regulators

- Packages

- Others

### AMD Catalog 1971

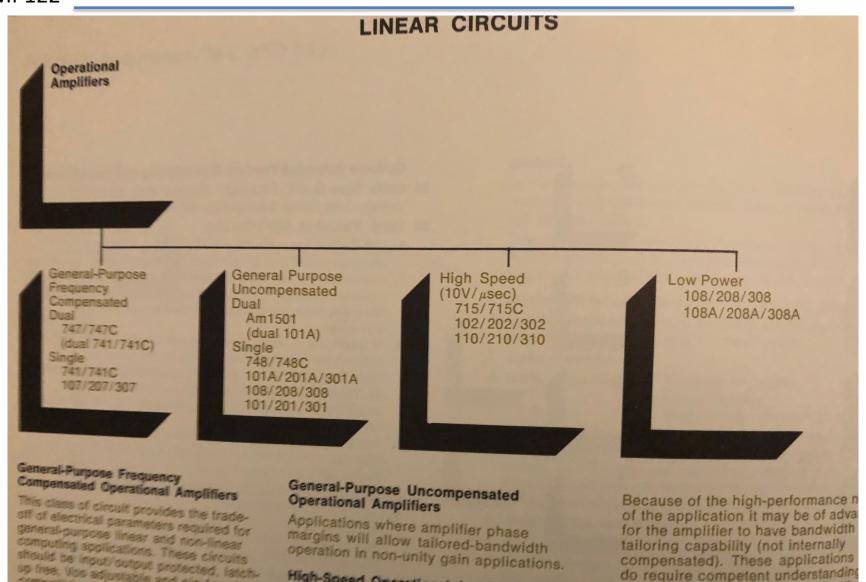

#### AMD Analog (Linear)

**COMP122**

up free. You adjustable and pin-for-pin-compatible with the 759.

margins will allow tailored-bandwidth operation in non-unity gain applications.

#### High-Speed Operational Amplifiers

The primary applications for these circuits are where in

compensated). These applications do require competent understandin of gain phase and compensation the

Low-Power Operational Amplifiers

### AMD Analog (Linear)

COMP122

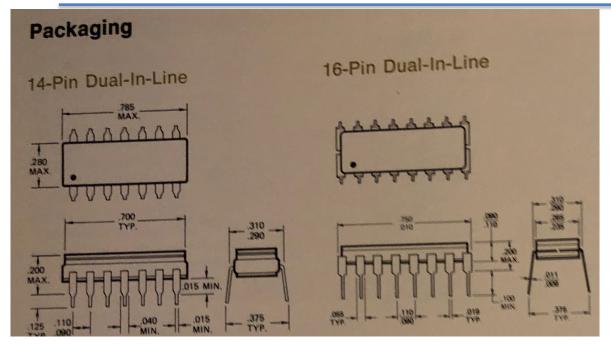

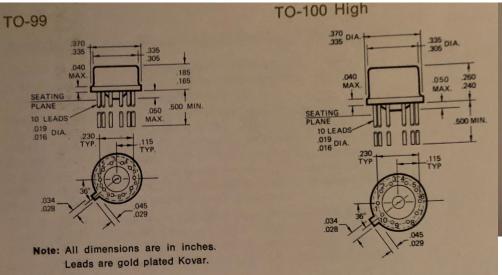

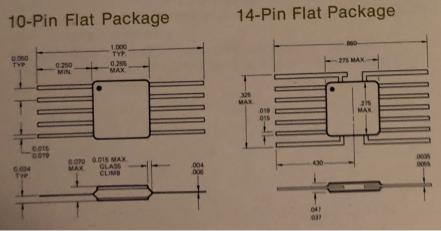

#### **AMD Packages**

COMP122

#### Section

## Logic

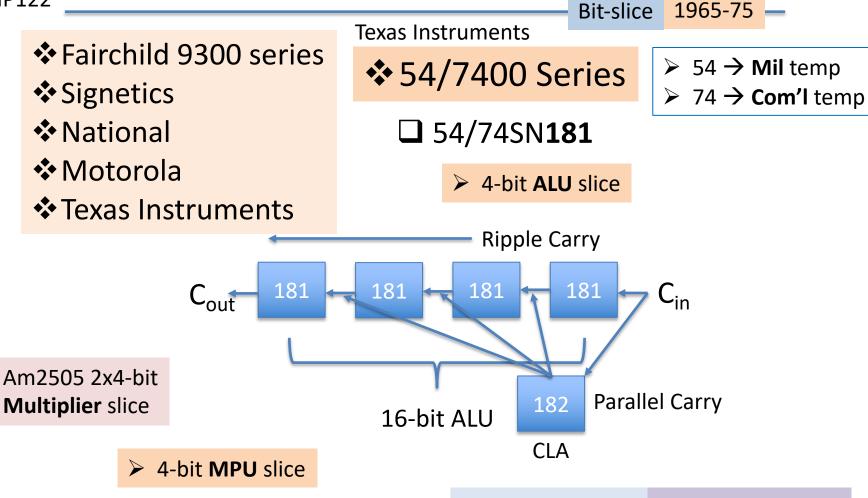

- Logic Product Lines

- **54/7400**

- F9300/Am9300

- ALU slice (4-bit)

- □ 54/74**181**

- Am9340

## **AMD Digital MSI**

COMP122

1971

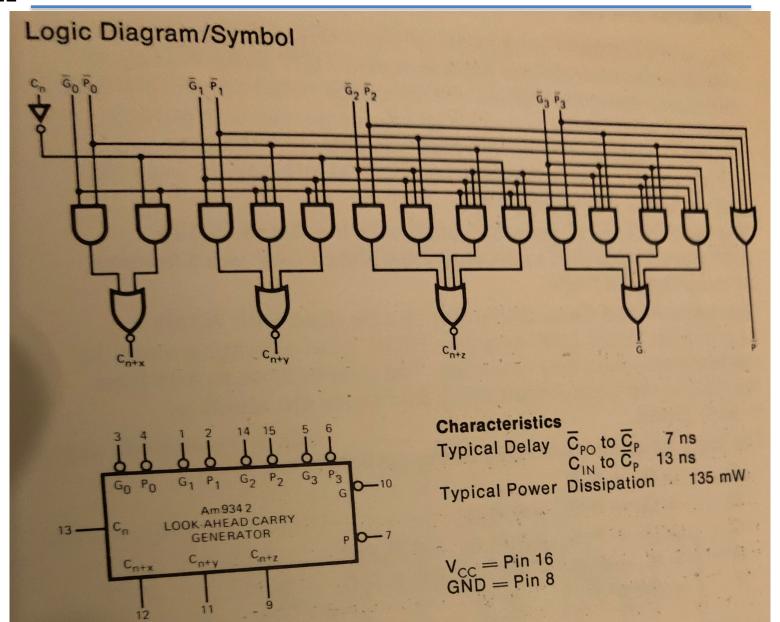

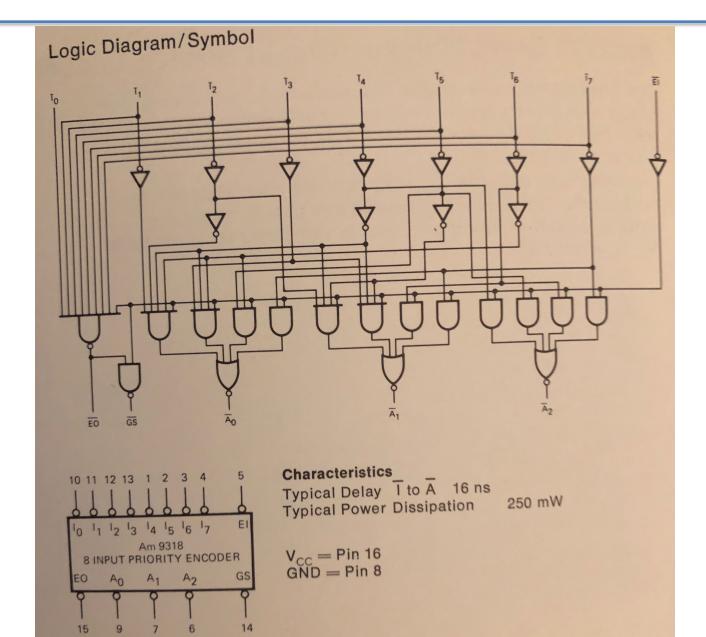

| Am MSI Registers Am9300 Am9328 Counters Am2501 Am8284 Am8285 Am9306 Am9310 Am9316 | Four-Bit Shift Register Dual Eight-Bit Shift Register  Binary Hexadecimal Up/Down C Binary Hexademical Up/Down C BCD Decade Synchronous Up/D BCD Decade Synchronous Up/D BCD Decade Counter Four-Bit Binary Counter | ounters                                                      |                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Encoders Am9318 Multiplexers Am9309 Am9312 Am9322 Latches Am9308 Am9314           | Eight-Input Priority Encoder                                                                                                                                                                                        | Am54/74182<br>Am9304<br>Am9324<br>Am9340<br>Am9341<br>Am9342 | 1 Four-Bit Arithmetic Logic Unit 2 Look-Ahead Carry Generator Dual Full Adder Five-Bit Comparator Four-Bit Arithmetic Logic Unit Four-Bit Arithmetic Logic Unit Carry Look Ahead d Demultiplexer Demultiplexer/One of Ten Decoder Demultiplexer/One of Sixteen Decoder |

### Logic IC's: ALU Slices

Replaced by **Am2900** family  $\rightarrow$  Am29**01**

Am29**10**

Am29**02**

ALU + Register file

microprogrammed

Microprogram sequencer

CLA

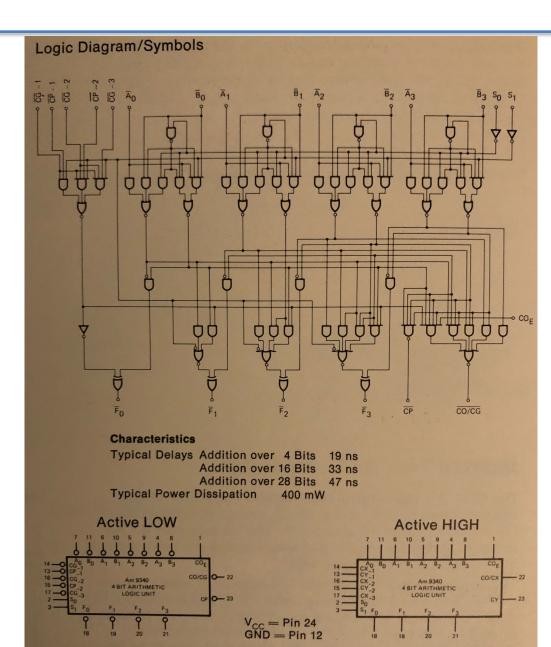

## AMD ALU - Am9340

#### AMD CLA – Am9342

COMP122

#### Section

# Logic

- PIC

- Muxes

- Decoders

- Logic functions

# PIC: Priority Interrupt Enc

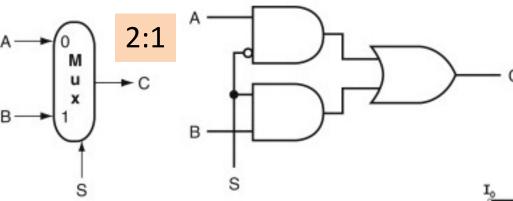

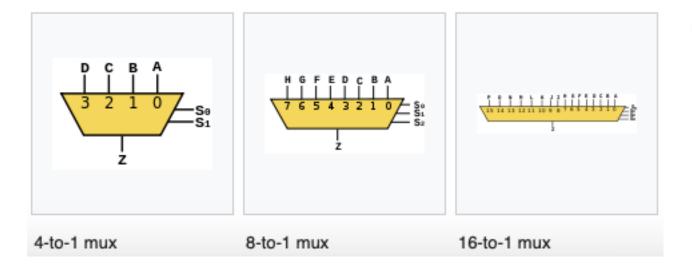

### **MUX**

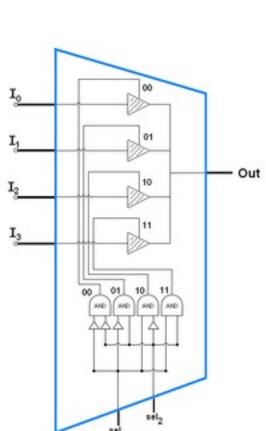

The following 4-to-1 multiplexer is constructed from 3-state buffers and AND gates

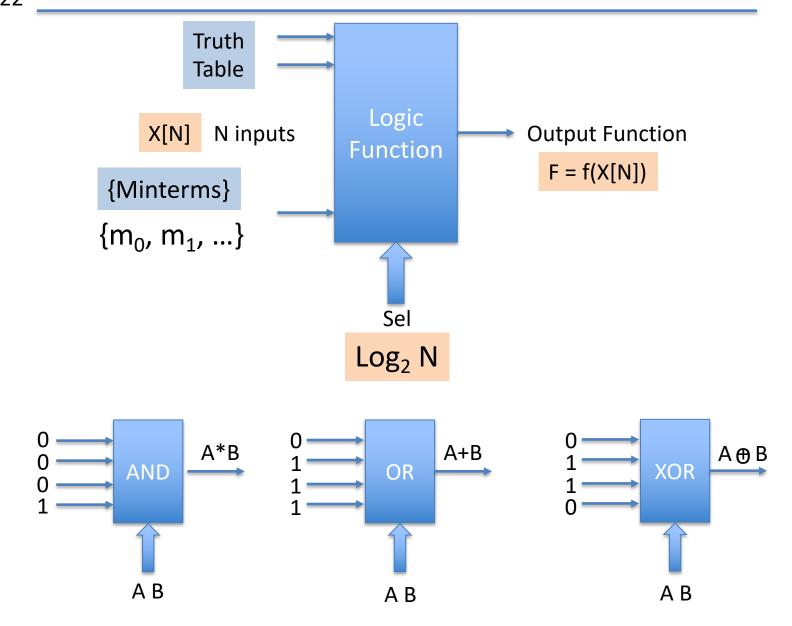

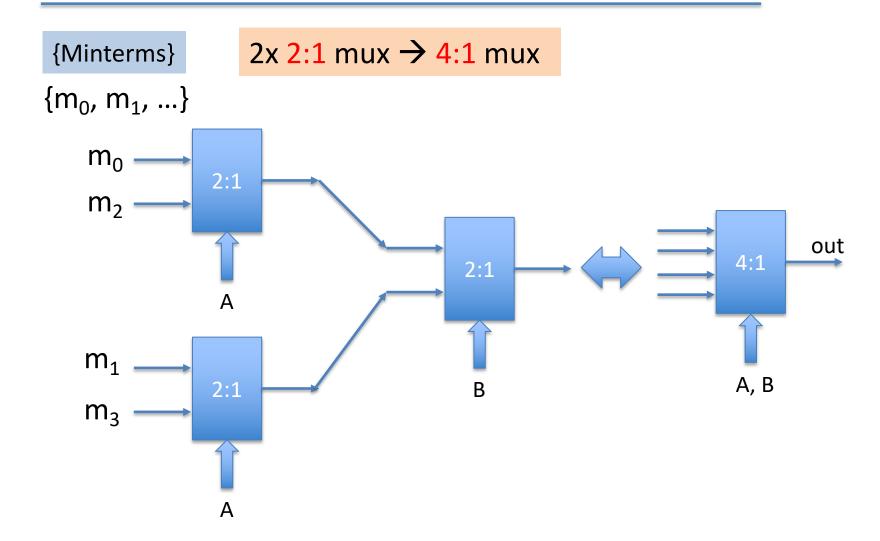

### MUX as Function Generator

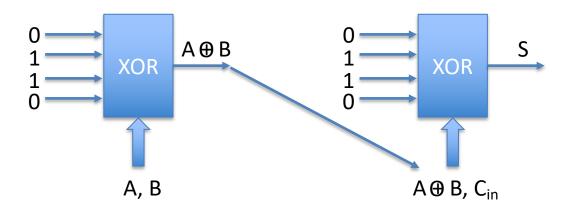

### Full Adder via Mux

$$S = A \oplus B \oplus C_{in}$$

### Mux Extension

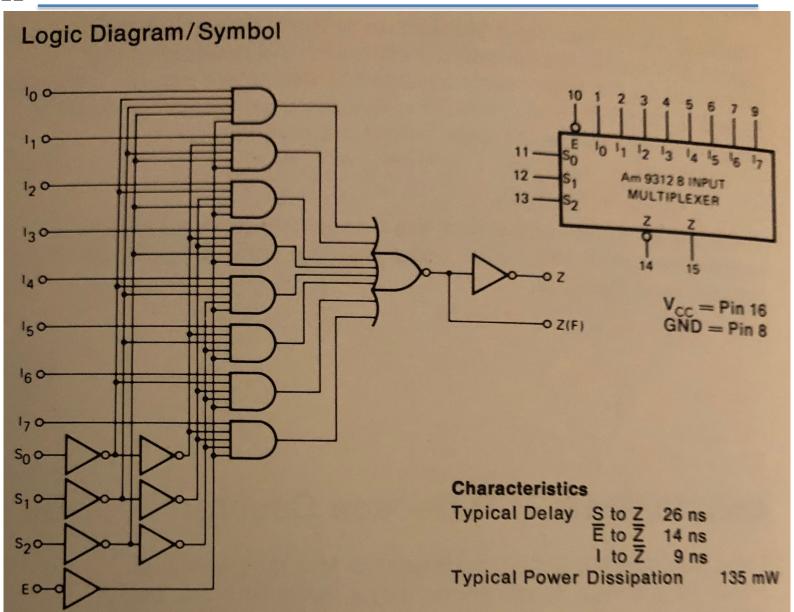

#### AMD 8:1 Mux

COMP122

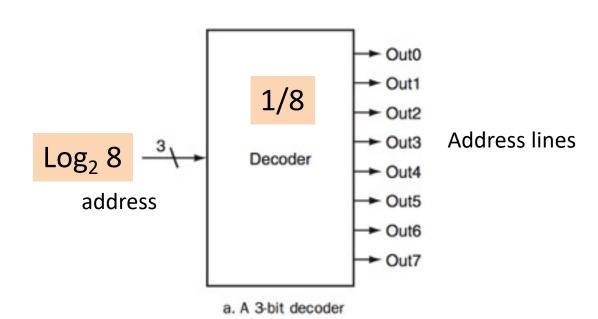

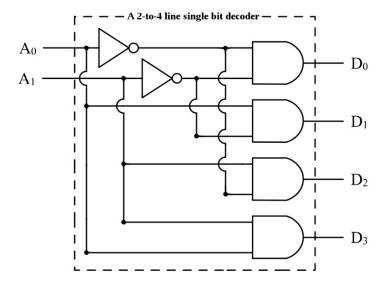

### Decoder

#### **Truth Table**

| $\mathbf{A}_1$ | $A_0$ | $D_3$ | $D_2$          | $\mathbf{D}_1$              | $\mathbf{D}_0$ |

|----------------|-------|-------|----------------|-----------------------------|----------------|

| 0              | 0     | 0     |                | 0                           | 1              |

| 0              | 1     | 0     | 0              | 1                           | 0              |

| 1              | 0     | 0     | 1              | 0                           | 0              |

| 1              | 1     | 1     | 0              | 0                           | 0              |

|                | 0     | 0 0   | 0 0 0<br>0 1 0 | 0 0 0 0<br>0 1 0 0<br>1 0 1 | 1 0 0 1 0      |

#### Minterm Equations

$$D_0 = \overline{A_1} \boldsymbol{\cdot} \overline{A_0}$$

$$D_1 = \overline{A_1} \boldsymbol{\cdot} A_0$$

$$D_2 = A_1 \boldsymbol{\cdot} \overline{A_0}$$

$$D_3 = A_1 \boldsymbol{\cdot} A_0$$

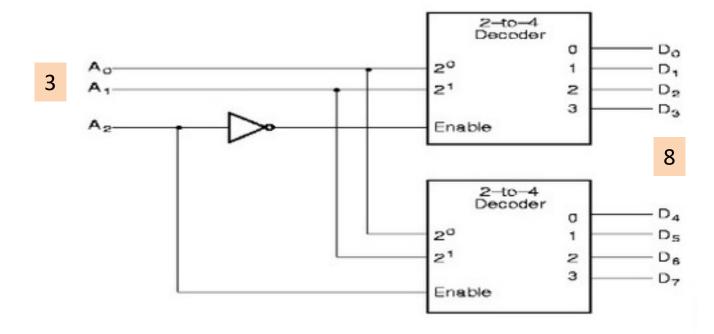

# **Decoder Expansion**

#### DECODER EXPANSION

$2x 2-to-4 \rightarrow 3-to-8 (1 of 8)$

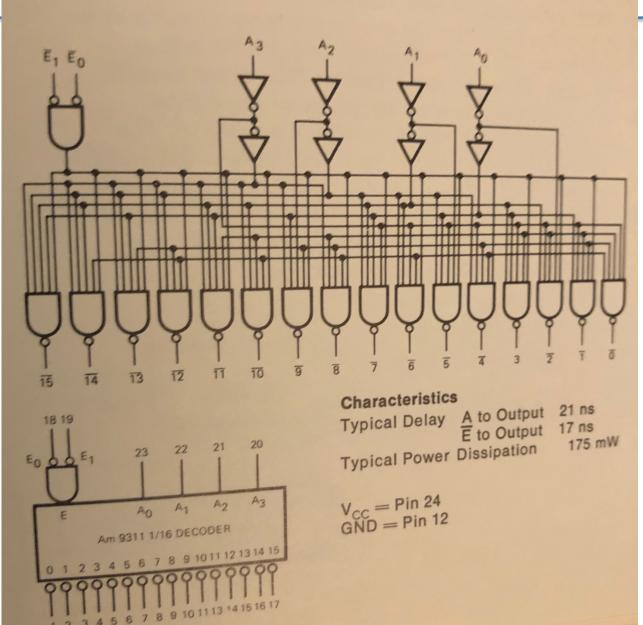

# Logic DAMD, Decoder (1/16)

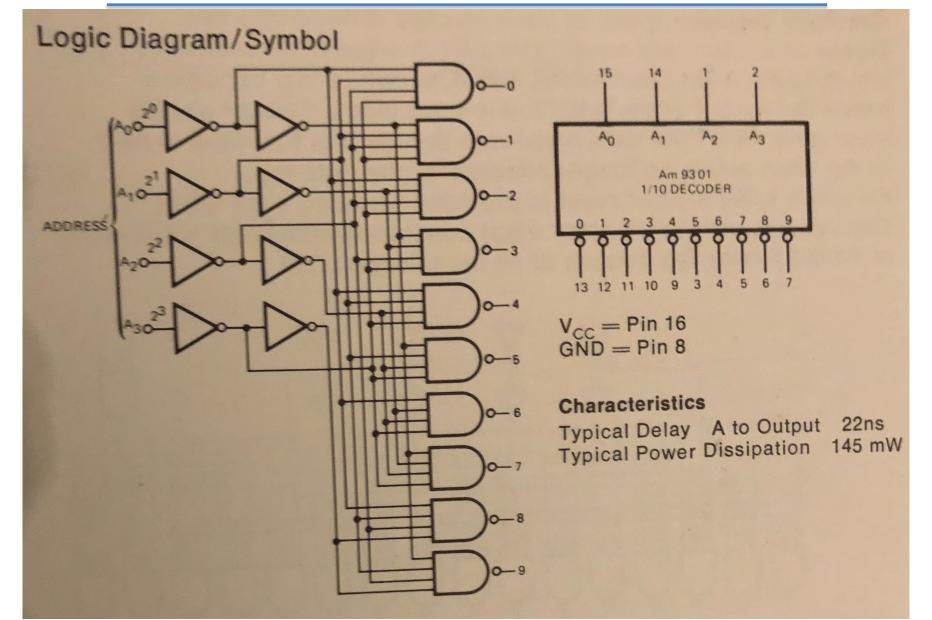

# AMD Decoder (1/10)

COMP122

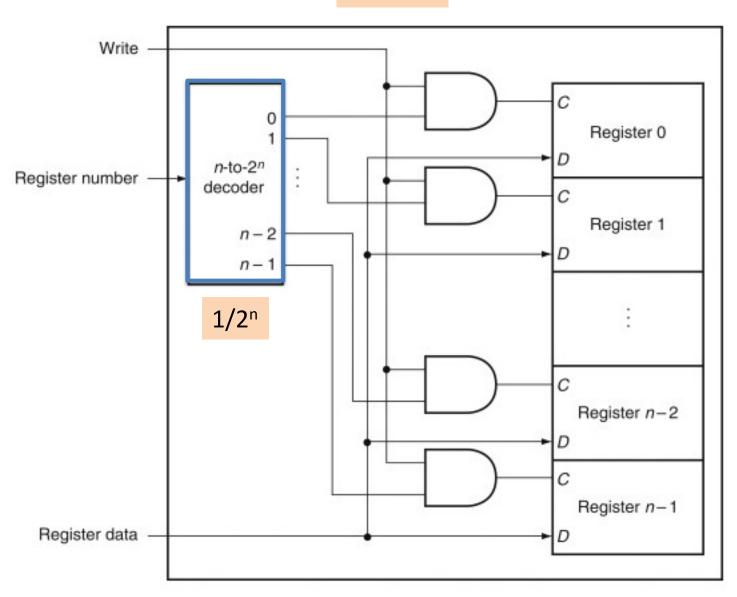

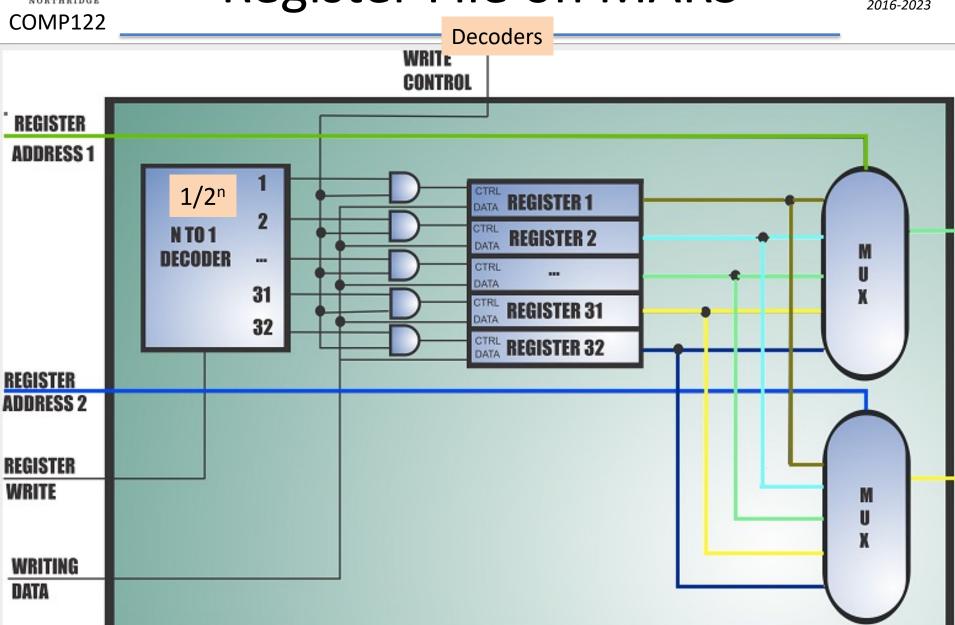

# Register File Input Side

Decoders

# Register File on MARS

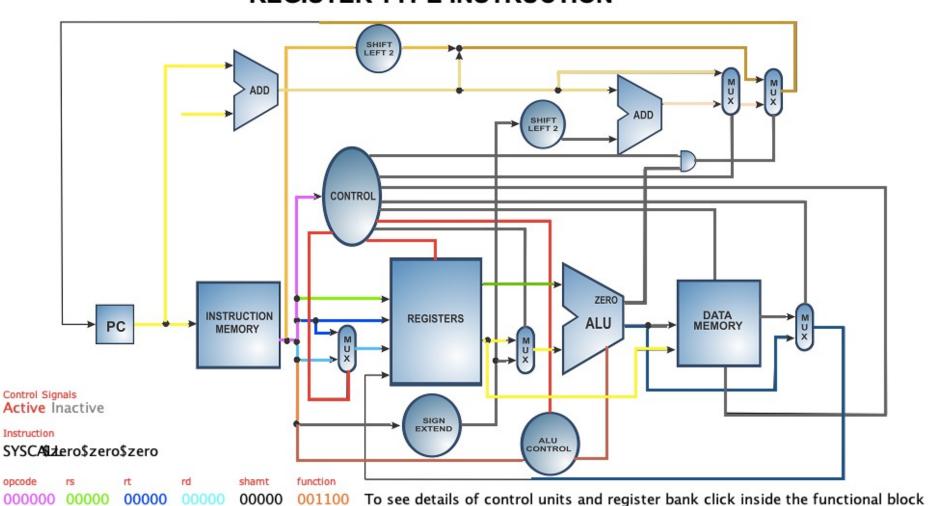

#### MIPS on MARS

#### REGISTER TYPE INSTRUCTION

#### Section

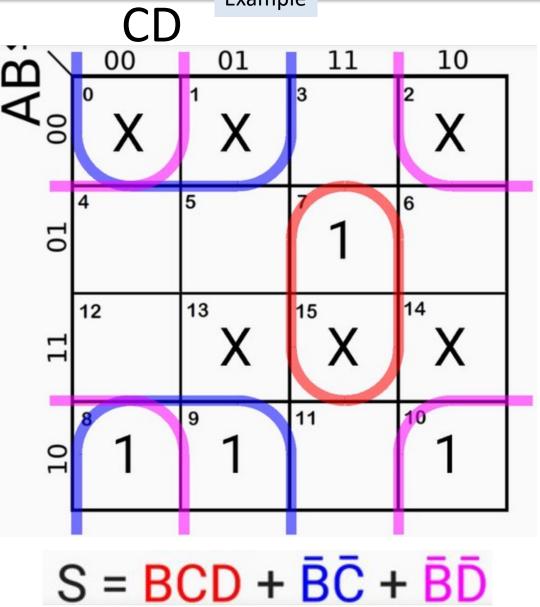

# Logic Minimization

# Head of Department (Electronics) a Government Polytechnic Nagpur Polytechnic Nagpur Encoder Example

COMP122 Quora

Related How do I make a converter (from excess 3 code to 8-4-2-1bcd code) using only 2-to -1 MUX and not gate?

The truth table for excess-3 code to binary code converter is given below. Being 0000, 0001, 0010 and 1101, 1110, 1111 as invalid excess-3 code, output is made don't care.

TRUTH TABLE

|                                  | IRUITI      | Nece           |

|----------------------------------|-------------|----------------|

|                                  | X3 X2 X1 X0 | B3 B2 B1 B0    |

|                                  | 0000        | AXXXX TINVALID |

|                                  | 0001        | ××××× Excess-3 |

|                                  | 0010        | ××××) code     |

|                                  | 0011        | 0000           |

| $B_0 = \{m4, m6, m8, m10, m12\}$ | } 0 1 0 0   | 0 0 0 1 0      |

| $B_1 = \{m5, m6, m9, m10\}$      | 0 1 1 0     | 0 100          |

| B <sub>2</sub> = {m7,m8,m9,m10}  | 1 0 0 0 1   | 0 1 1 0        |

| $B_3 = \{m11, m12\}$             | 1 0 1 1     | 1 0 0 1        |

|                                  | , 101       | X X X A Excess |

|                                  | 1 1 1 0     | × × × × Code   |

|                                  | 1 1 11      | × × × ×        |

# Logic Function Minimization

Combinational

- Quine-McKluskey

- ☐ Prime implicants

- ☐ Essential Pl's

❖ Karnaugh ("K") Maps

0

Sum of Products: minterms

General form  $F(x, y) = \{m_0, m_1, m_2, m_3\}$

Example

$$F(x, y) = \{m_0, m_1\} = x'y' + xy' \rightarrow y'$$

#### Quora COMP122

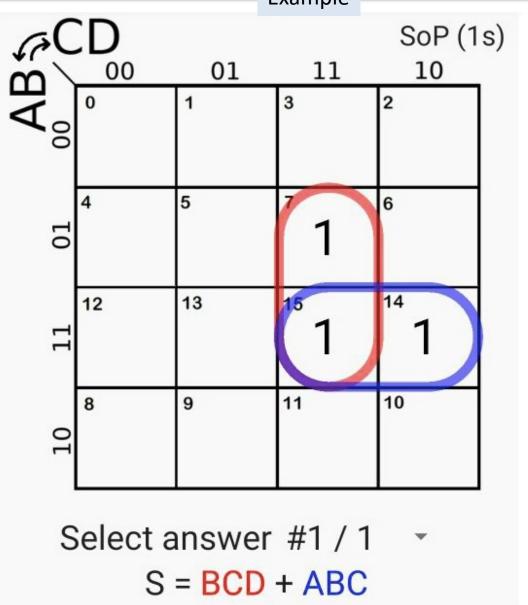

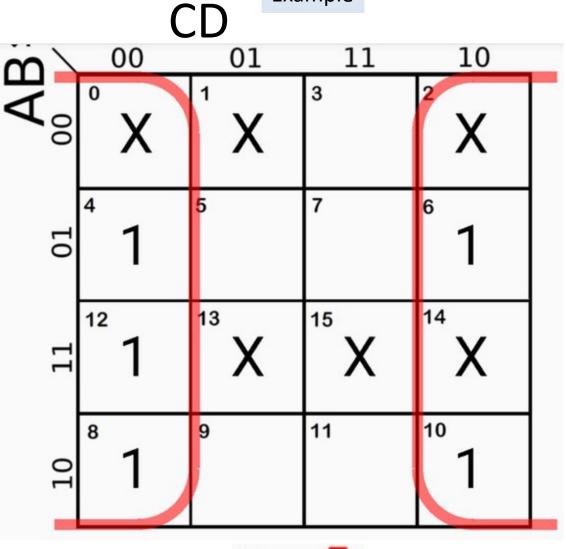

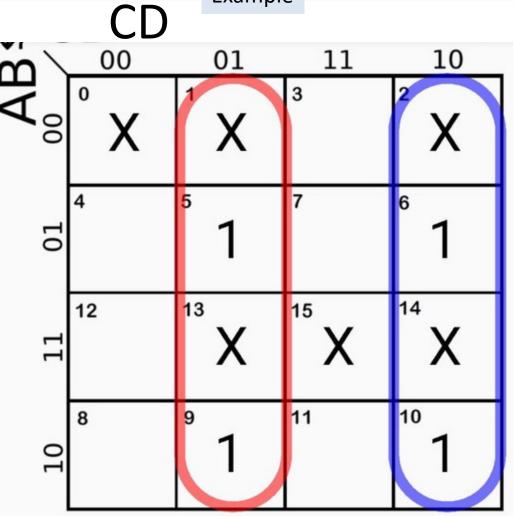

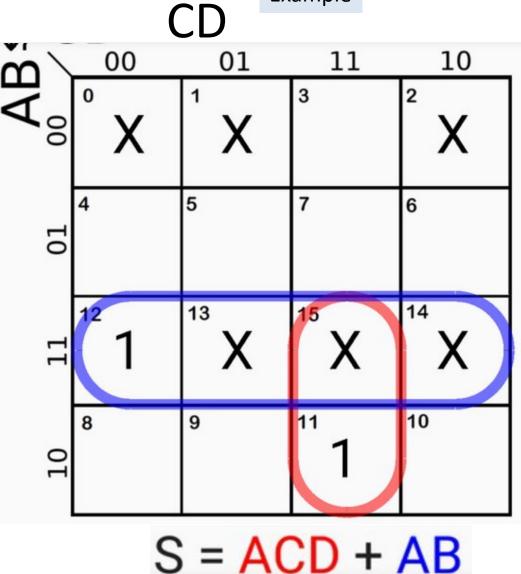

# K-Maps

Example

**Gray codes**

Quora COMP122

Example

Gray codes

$$S = \overline{D}$$

Quora

Example

Gray codes

$$S = \overline{C}D + C\overline{D}$$

Quora

Example

**Gray codes**

Quora

Example

Gray codes

#### Section

# Memory

- □ SRAM

- DRAM

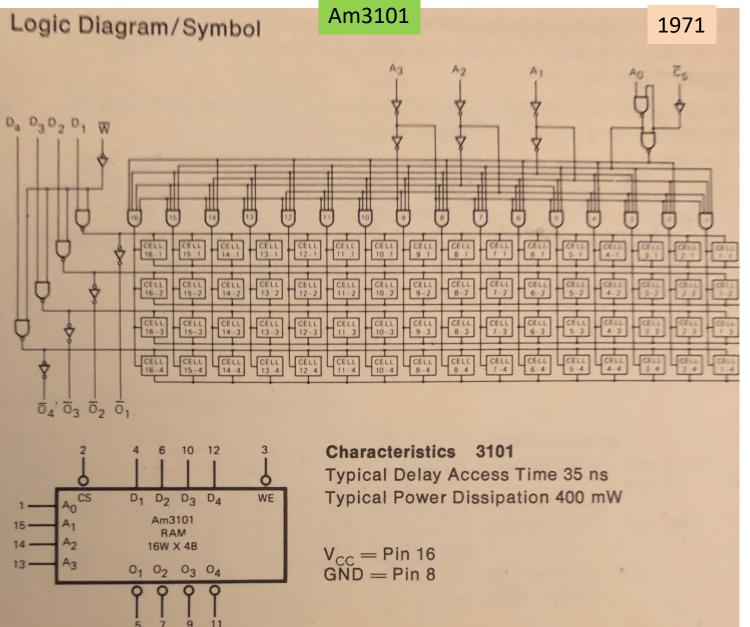

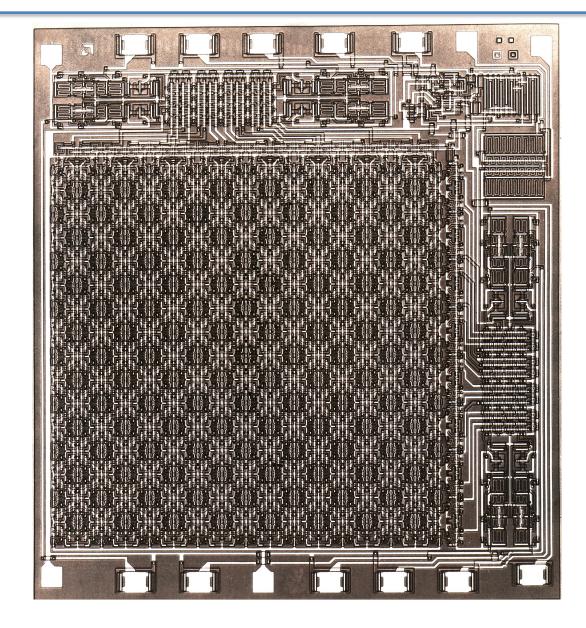

### AMD 64-Bit Bipolar SRAM

DR JEFF SOFTWARE NDIE APP DEVELOPER © Jeff Drobman 2016-2023

COMP122

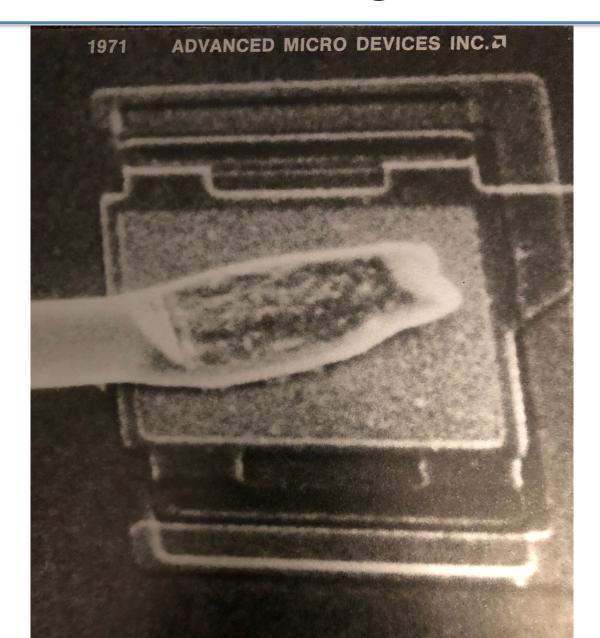

### AMD MOS LSI

**COMP122**

1971

MOS is a technology of today as well as tomorrow. Various MOS technologies have been developed, but we feel silicon gate to be the most promising. Silicon gate will be the primary technology used for memory application MOS products from Advanced Micro Devices. The basis for this decision is:

- 1. It is directly TTL and DTL compatible

- 2. It has greater speed than conventional metal-gate MOS

- 3. It is more reliable

- 4. Its reproducibility is higher

- 5. It is lower cost on a per-function basis

Our commitment in MOS is to produce large-chip standard circuits. The circuits are to have a broad customer base, and be available in full military temperature range (-55°C to +125°C) as well as the commercial temperature range (0°C to +75°C). Future plans call for the following additions to our product line in 1971:

256-Bit Static Random Access Memory

1024-Bit Dynamic Two-Phase Shift Register (1024x1, 512x2, 256x4)

1024-Bit Dynamic Random Access Memory

### Am1101A 256x1 SRAM

# DRAM (AMD 1Kx1)

Am1103A 1971

#### Section

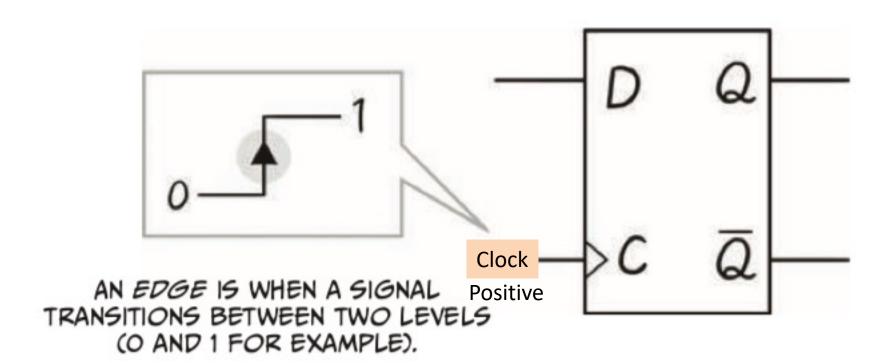

# Logic

- Sequential

- Flip-flops

- Latches

- Counters

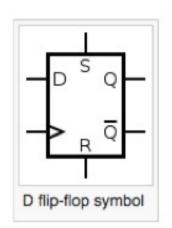

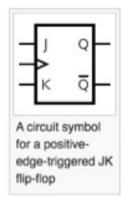

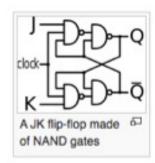

# Sequential Logic: Flip-Flops

Clocked

# Sequential Logic: Flip-Flops

#### [from Wikipedia]

| Clock       | D | Q <sub>next</sub> |

|-------------|---|-------------------|

| Rising edge | 0 | 0                 |

| Rising edge | 1 | 1                 |

| Non-Rising  | X | Q                 |

"D" FF

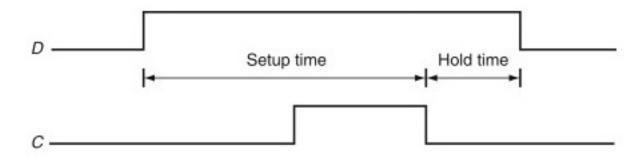

Timing: setup, hold, delay

#### Other FFs

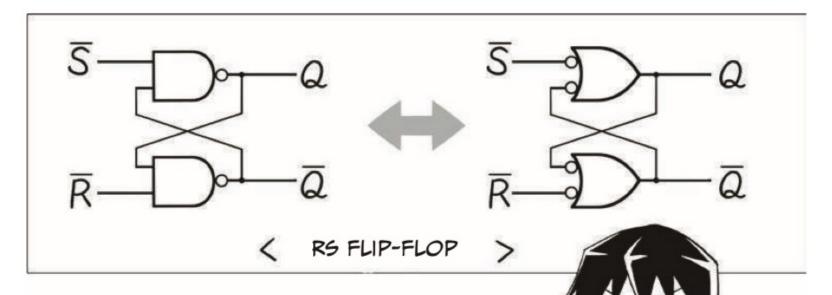

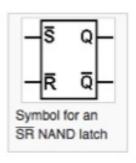

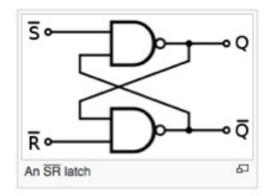

# Sequential Logic: SR Latch

| INP | INPUTS         |             | PUTS       | FUNCTION                      |

|-----|----------------|-------------|------------|-------------------------------|

| S   | $\overline{R}$ | Q           | ā          |                               |

| 1   | 1              | DOES<br>CHA | NOT<br>NGE | RETAINS ITS<br>CURRENT OUTPUT |

| 0   | 1              | 1           | 0          | SET                           |

| 1   | 0              | 0           | 1          | RESET                         |

| 0   | 0              | 1           | 1          | NOT ALLOWED                   |

NOTE THAT S AND

R HAVE NEGATION

SYMBOLS! THIS IS CALLED

ACTIVE-LOW, AND IT MEANS

THEY ARE ACTIVATED WHEN

THE INPUT VOLTAGE IS

LOW (O) INSTEAD OF

HIGH (1).

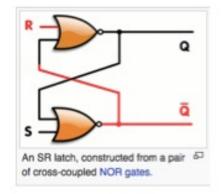

# Sequential Logic: Latches

| SR latch operation |   |             |  |

|--------------------|---|-------------|--|

| s                  | R | Action      |  |

| 0                  | 0 | not allowed |  |

| 0                  | 1 | Q = 1       |  |

| 1                  | 0 | Q = 0       |  |

| 1                  | 1 | No Change   |  |

#### [from Wikipedia]

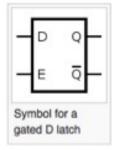

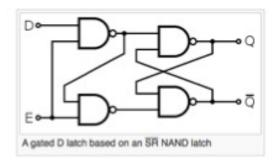

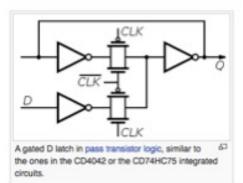

#### Gated D latch truth table

| E/C | D | Q                 | Q                              | Comment   |

|-----|---|-------------------|--------------------------------|-----------|

| 0   | X | Q <sub>prev</sub> | $\overline{\mathbf{Q}}_{prev}$ | No change |

| 1   | 0 | 0                 | 1                              | Reset     |

| 1   | 1 | 1                 | 0                              | Set       |

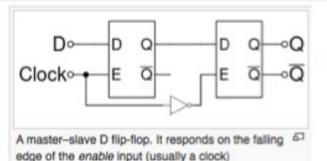

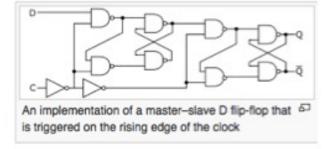

# Clocking

When the clock goes from low to high (0 to 1), we see a rising edge, and when it goes back from high to low (1 to 0), we see a falling edge.

| RISING EDGE                             | FALLING EDGE                            |  |

|-----------------------------------------|-----------------------------------------|--|

|                                         |                                         |  |

|                                         |                                         |  |

| WHEN THE CLOCK GOES<br>FROM LOW TO HIGH | WHEN THE CLOCK GOES<br>FROM HIGH TO LOW |  |

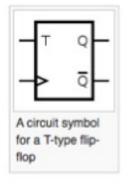

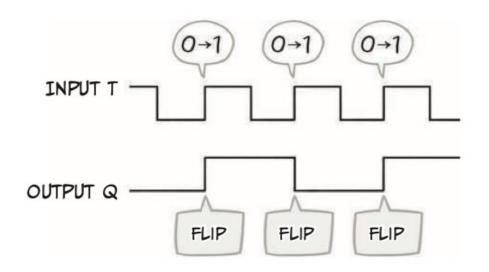

# T: Toggle Flip-flop

Fuhahaha! Like I would ever forget! The *T flip-flop* only has one input, as you can see, and is pretty simple. Whenever the input T changes from 0 to 1, or 1 to 0, the output stored in Q flips state. It looks something like this time chart.

THERE ARE T FLIP-FLOPS THAT ACTIVATE JUST ON FALLING EDGES INSTEAD (1 TO 0).

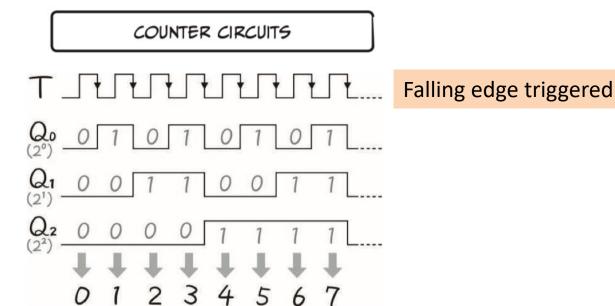

## Counter

COMP122

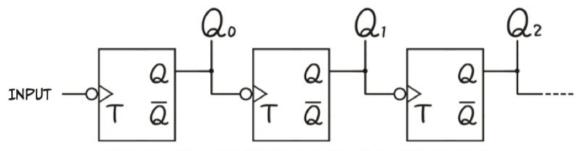

Toggle

By the way, flipping between 1 and 0 is called *toggling*. The *T* in T flip-flop actually stands for *toggle*! Also, by connecting several T flip-flops together as in the schematic below, you can make a circuit that can count—a counter circuit.

THIS CIRCUIT SHOWS HOW SEVERAL T FLIP-FLOPS TOGGLED BY THE FALLING EDGE OF AN INPUT SIGNAL CAN ACT AS A COUNTER.

## Counter

#### Counter

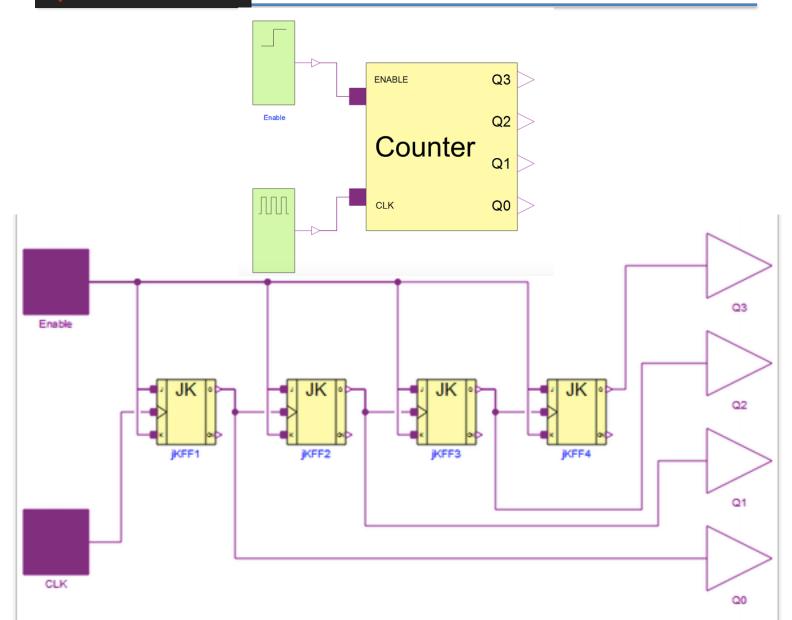

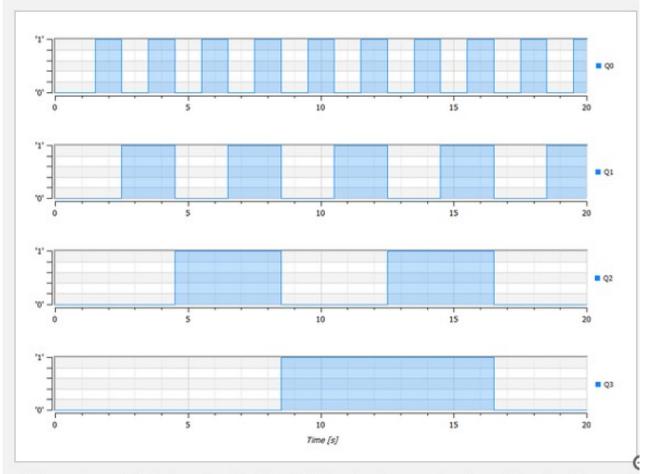

The counter in this example is a 4-bit asynchronous counter based on JK flip-flops. The flip-flops are connected with both their J and K terminals to the enable pin, putting them in "toggle mode". The flip-flop to the left, producing the Q0 signal, will change its output state for each falling edge of the clock signal, for example, a CPU clock. Since the output toggles for each falling edge of the clock, the clock toggles twice for each toggle of the output.

This diagram from a simulation shows how the logic levels of the four bits change over time. The enable signal goes from 0 to 1 after one second.

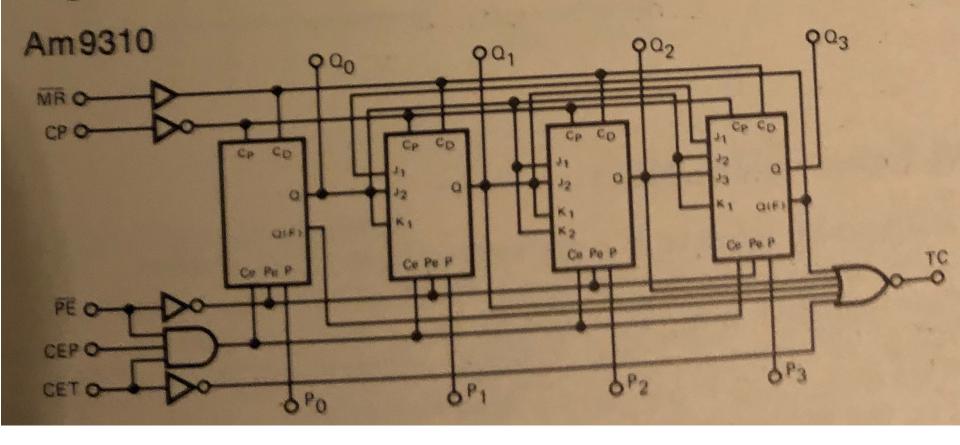

## **AMD Counter**

Logic Diagrams/Symbol

## Section

# Logic

- Multiplication

- Division

#### Ancient Egyptian multiplication

From Wikipedia, the free encyclopedia

(Redirected from Russian peasant algorithm)

In mathematics, ancient Egyptian multiplication (also known as Egyptian multiplication, Ethiopian multiplication, Russian multiplication, or peasant multiplication), one of two multiplication methods used by scribes, was a systematic method for multiplying two numbers that does not require the multiplication table, only the ability to multiply and divide by 2, and to add. It decomposes one of the multiplicands (preferably the smaller) into a sum of powers of two and

Ancient **Peasant** Multiplication

## Multiplication

Quora

Jeff Drobman · Just now

multiplication is usually done completely in hardware, via a 2D array of "XY(i) + C" multiplier modules, whereby each row generates a partial product of the next signed digit of the multiplier times the multiplicand. shifting occurs in the hardware placement of each row. this array can also be pipelined, so multiple operations can be performed in sequential concurrency.

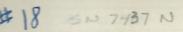

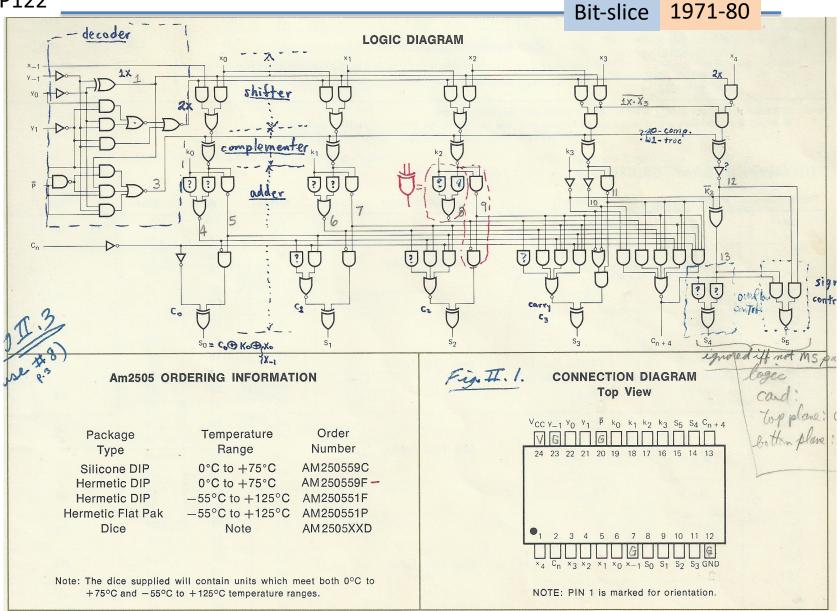

(See the 1971 **Am2505** 2x4-bit multiplier slice, and my personal MS thesis.)

Ancient **Peasant** Multiplication

# How do I write an ARM (Assembly) program that determines the product of 2 numbers using Russian peasant multiplication?

Jeff Drobman · just now

Former Stock Trader and App Developer (2003-present)

first learn ARM assembly language. then, follow this algorithm:

- determine the smaller operand (use a "compare" op) and make it the multiplier

- create a table of 2x the larger operand (multiplicand)

- sum the table entries where the binary bit position is 1, and skip the 0's.

#### Examples [edit]

This example uses peasant multiplication to multiply 11 by 3 to arrive at a result of 33.

13x238

| Dec | imal:              | Binary:                       | 3x11 | 13 | 238   | 110 <mark>1</mark> | (13)           | 11101110              | (238)            |

|-----|--------------------|-------------------------------|------|----|-------|--------------------|----------------|-----------------------|------------------|

| 11  | 3                  | 1011 11                       | SKII | 6  | 476   | <del>110</del>     | <del>(6)</del> | <del>11101110</del> 0 | <del>(476)</del> |

| 2   | 6<br><del>12</del> | 101 110<br>10 <del>1100</del> |      | 3  | 952   | 11                 | (3)            | <b>11101110</b> 00    | (952)            |

| 1   | 24                 | 1 11000                       |      | 1  | +1904 | 1                  | (1)            | <b>11101110</b> 000   | (1904)           |

|     | 33                 | 100001                        |      | -  | 3094  |                    |                |                       |                  |

# 2's Complement Multiply

#### **❖**Simple

- Convert Multiplier to positive if negative

- Invert Multiplicand (if needed)

#### ❖ Booth's algorithm

- Use Multiplier as encoded by BA (groups of 2)

- Leave Multiplicand as is

Booth's multiplication algorithm is a multiplication algorithm that multiplies two signed binary numbers in two's complement notation. The algorithm was invented by Andrew Donald Booth in 1950 while doing research on crystallography at Birkbeck College in Bloomsbury, London. Booth's

**COMP122**

Signed 2'sC Multiplication

#### Booth's multiplication algorithm

**Booth's Recoding**

From Wikipedia, the free encyclopedia

**Booth's multiplication algorithm** is a multiplication algorithm that multiplies two signed binary numbers in two's complement notation. The algorithm was invented by Andrew Donald Booth in 1950 while doing research on crystallography at Birkbeck College in Bloomsbury, London.<sup>[1]</sup> Booth's algorithm is of interest in the study of computer architecture.

#### The algorithm [edit]

Booth's algorithm examines adjacent pairs of bits of the 'N'-bit multiplier Y in signed two's complement representation, including an implicit bit below the least significant bit,  $y_{-1} = 0$ . For each bit  $y_i$ , for i running from 0 to N - 1, the bits  $y_i$  and  $y_{i-1}$  are considered. Where these two bits are equal, the product accumulator P is left unchanged. Where  $y_i = 0$  and  $y_{i-1} = 1$ , the multiplicand times  $2^i$  is added to P; and where  $y_i = 1$  and  $y_{i-1} = 0$ , the multiplicand times  $2^i$  is subtracted from P. The final value of P is the signed product.

The representations of the multiplicand and product are not specified; typically, these are both also in two's complement representation, like the multiplier, but any number system that supports addition and subtraction will work as well. As stated here, the order of the steps is not determined. Typically, it proceeds from LSB to MSB, starting at i = 0; the multiplication by  $2^i$  is then typically replaced by incremental shifting of the P accumulator to the right between steps; low bits can be shifted out, and subsequent additions and subtractions can then be done just on the highest N bits of P. There are many variations and optimizations on these details.

The algorithm is often described as converting strings of 1s in the multiplier to a high-order +1 and a low-order -1 at the ends of the string. When a string runs through the MSB, there is no high-order +1, and the net effect is interpretation as a negative of the appropriate value.

1-strings

0111..1 = 1000..0 - 1

**Signed 2'sC** Multiplication — Drobman MS Thesis —

Booth's Recoding

| y <sub>i+l</sub>                           | yi              | y <sub>i-1</sub> | y <sub>i+l</sub> | y <sub>i</sub>  | M,        | Operation                                                            |  |  |  |  |

|--------------------------------------------|-----------------|------------------|------------------|-----------------|-----------|----------------------------------------------------------------------|--|--|--|--|

| 00001111                                   | 0 0 1 1 0 0 1 1 | 010101           | 0001111000       | 0 1 1 0 0 1 1 0 | 011201110 | add O add X add X add 2X subtract 2 subtract X subtract X subtract X |  |  |  |  |

| *bits recoded as a 1-string transformation |                 |                  |                  |                 |           |                                                                      |  |  |  |  |

|                                            |                 |                  | TABLE            | 2.1             |           |                                                                      |  |  |  |  |

Signed 2'sC Multiplication — Booth's Recoding —

UNIVERSITY OF CALIFORNIA Los Angeles

**Drobman MS Thesis** 1973

> Theory and Design of a High Speed, Two's Complement Arithmetic Unit Using an Array of Digital Multiplier Modules

A thesis submitted in partial satisfaction of the requirements for the degree Master of Science in Computer Science

by

Jeffrey Howard Drobman

COMP122

**Signed 2'sC** Multiplication

Drobman MS Thesis -

2.3.2 Booth's Algorithm

**Booth's Recoding**

The discussion, so far, has been restricted to multipliers in magnitude representation. The concepts developed can be extended, however, to multipliers in two's complement as well. In fact, a simple recoding scheme for two's complement multipliers was developed some time ago by A. D. Booth and K. H. V. Booth, as described in Chu [6]. Booth's Algorithm (as it is commonly called) involves a recoding of the type described in the previous section with k = 1, with the important exception that when the most significant bit is a member of a 1-string, the multiplier is not extended -- due to its being in two's complement. Ignoring this extension preserves implicit value for two's complement multipliers, quite unlike the case of its mag-(2.2.19).)

Booth's Algorithm is merely the recoding scheme itself, and Chu's presentation [6] starts with the recoding scheme and then work back to the original expression. While this does prove Booth's Alback to the original expression.

COMP122

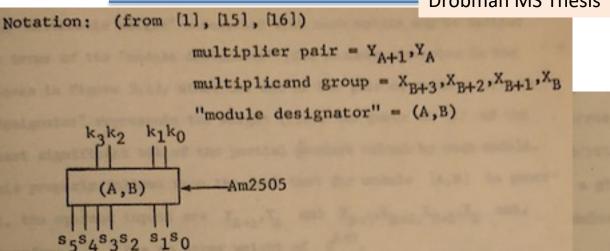

Bit-slice

1971-80

Four-Bit by Two-Bit 2's Complement Multiplier

Advanced Micro Devices

Complex Digital Integrated Circuits

#### **Distinctive Characteristics:**

- Provides 2's complement multiplication at high speed without correction.

- Can be used in an iterative scheme or time sequenced mode.

- Multiplies two 12-bit signed numbers in typically 200ns.

- Multiplies in active HIGH (positive logic) or active LOW (negative logic) representations.

- Easy correction for unsigned, sign-magnitude or 1's complement multiplication.

- 100% reliability assurance testing in compliance with MIL STD 883.

#### **FUNCTIONAL DESCRIPTION:**

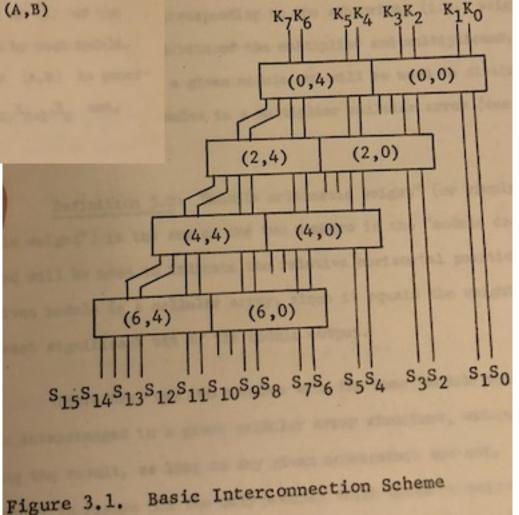

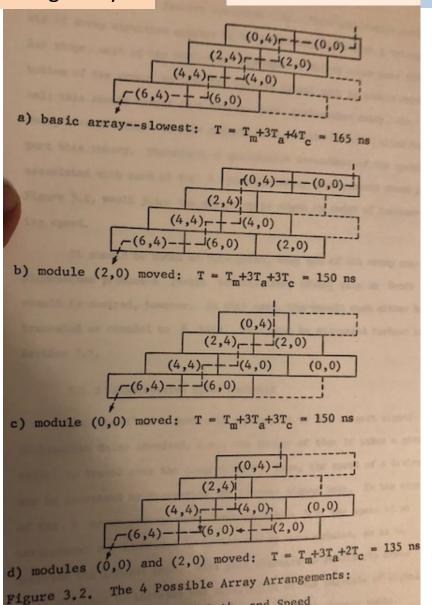

The Am2505 is a high-speed digital multiplier that can multiply numbers represented in the 2's complement notation and produce a 2's complement product without correction. The device consists of a 4x2 multiplier that can be connected to form iterative arrays able to multiply numbers either directly, or in a time sequenced arrangement. The device assumes that the most significant digit in a word carries a negative weight, and can therefore be used in arrays where the multiplicand and multiplier have different word lengths. The multiplier uses the guaternary algorithm and performs the function S = X Y + K where K is the input field used to add partial products generated in the array. At the beginning of the array the K inputs are available to add a signed constant to the least significant part of the product. Multiplication of an m bit number by an n bit number in an array results in a product having m+n bits so that all possible combinations of product are accounted for. If a conventional 2's complement product is required the most significant bit can be ignored, and overflow conditions can be detected by comparing the last two product digits.

number of connection schemes are possible. Figure 4 shows diagramatically the connection scheme that results in the fastest multiply. If higher speed is required an array can be split into several parts, and the parts added with high-speed look-ahead carry adders such as the Am9340.

Provision is made in the design for multiplication in the active high (positive logic) or active low (negative logic) representations simply by reinterpreting the active level of the input operands, the product, and a polarity control P. For a more complete description and applications the user is referred to the Am2505 Application Note.

####

COMP122

S== (p-= 1)c + 7- 1-

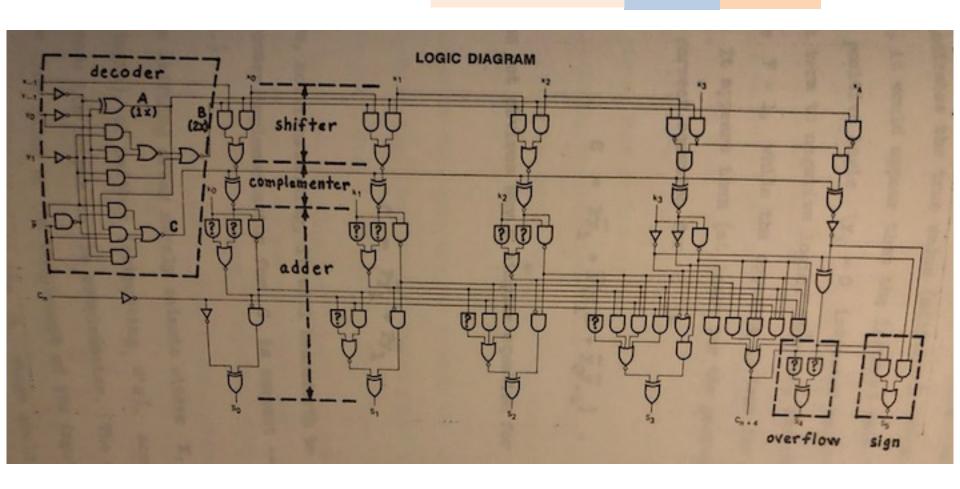

COMP122 Drobman MS Thesis - Bit-slice

1971-80

**Drobman MS Thesis**

Bit-slice

1971-80

**Drobman MS Thesis**

Bit-slice

1971-80

2x4-bit slices

8-bit x 8-bit multiply

COMP122

**Timing Analysis**

**Drobman MS Thesis**

Bit-slice

1971-80

Non-Restoring Div

#### How do calculators calculate binary division?

Jeff Drobman, Lecturer at California State University, Northridge (2016-present)

Answered just now

the most common division algorithm used in the past was "non-restoring". but there are others, as listed in Wikipedia:

"Division algorithms fall into two main categories: slow division and fast division. Slow division algorithms produce one digit of the final quotient per iteration. Examples of slow division include restoring , non-performing restoring, non-restoring , and SRT division. Fast division methods start with a close approximation to the final quotient and produce twice as many digits of the final quotient on each iteration. Newton-Raphson and Goldschmidt algorithms fall into this category."

Quora

Simple

Here's one way to implement the iterative approach: (There are others...)

- Align the leading 1s of the significands. ☐ This is usually easy in floating point they're already aligned by the format, unless one or both of the numbers is subnormal (aka. denormal). ☐

- 2. Compare the dividend and the divisor.

- a. If the dividend is not smaller than the divisor, subtract the divisor from the dividend and write a 1.

- b. Otherwise, don't subtract, and write a 0.

- 3. Shift the dividend (or what remains of it) left by 1 bit.

- 4. Repeat steps 2 and 3 until you have sufficient quotient bits—namely, that you have a 1 in the "hidden 1" position of the quotient.

#### Quora

The original Pentium implemented a faster iterative approach that produced 2 bits per iteration: Radix-4 SRT division. ☑ I won't go into the details of the algorithm. I will point out three salient features:

- It recodes the numbers into a redundant representation, meaning that each bit of the inputs expand to multiple bits in the recoded representation. The redundant representation allows deferring carries and borrows.

- 2. It uses a large lookup table to decide what action to take at each step.

- 3. Rather than just producing 2 bits of quotient per iteration, it actually produces one of 5 values at each step: -2, -1, 0, +1, +2. Later steps can refine errors introduced in earlier steps.

The infamous Pentium FDIV bug ☑ arose from the lookup table mentioned above: There were 5 missing +2 entries in the lookup table on the buggy versions of the Pentium.

SRT division is a nice speedup, but it's only a linear speedup. That is, it doubles the speed. Double precision is still around twice as expensive as single precision.

Quora

As transistors have gotten cheaper, modern hardware has turned to even faster approaches:

- Newton-Raphson division  $\square$  works by iterating Newton's root-finding method on  $f(x) = \frac{1}{x} d$  to find the reciprocal of the divisor d. Once you find that, you multiply the dividend by that reciprocal. The infamous Quake 3 Hack  $\square$  is based on this approach, although in that case it was inverse square root rather than an ordinary divide.

- Goldschmidt division works a little differently. Multiply both dividend and divisor by a common factor F. F is chosen to push the divisor toward 1.0. Repeat until the divisor is close enough to 1, and stop. If you choose the common factor properly, this converges quickly. AMD processors since Athlon use this approach.

What's neat about Newton-Raphson and Goldschmidt approaches is that both converge quadratically when implemented properly. That is, each iteration doubles the number of valid bits in the result estimate. That means single precision results come after just a few iterations, and double precision computations usually only require one additional iteration.

#### Section

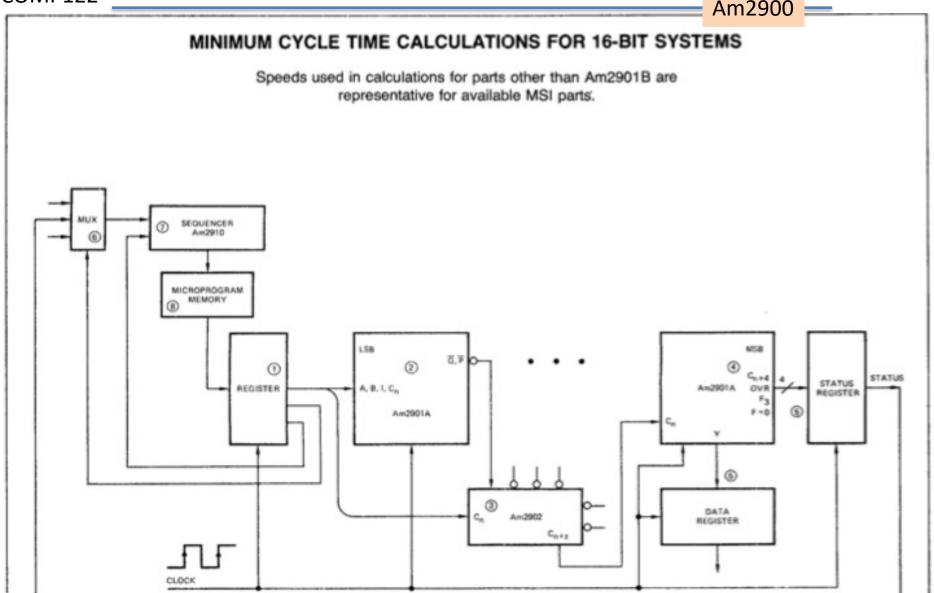

# Logic Timing

- Am2900

- Combinational

- Prop delays

- Sequential

- Setup times

- Hold times

# Sync Timing (AC)

# Timing – Cycle Times

**COMP122**

Am2900

# **Timing**

Am2900

#### B. Combinational Propagation Delays. $C_L = 50 pF$

| To Output<br>From Input   | Y  | F3 | Cn+4 | G, P | F=0 | OVR | RAM0<br>RAM3 | Q0<br>Q3 |

|---------------------------|----|----|------|------|-----|-----|--------------|----------|

| A, B Address              | 60 | 61 | 59   | 50   | 70  | 67  | 71           | -        |

| D                         | 38 | 36 | 40   | 33   | 48  | 44  | 45           | -        |

| Cn                        | 30 | 29 | 20   | -    | 37  | 29  | 38           | -        |

| 1012                      | 50 | 47 | 45   | 45   | 56  | 53  | 57           | -        |

| 1345                      | 51 | 52 | 52   | 45   | 60  | 49  | 53           | -        |

| 1678                      | 28 | -  | -    | -    |     | -   | 27           | 27       |

| A Bypass ALU<br>(I = 2XX) | 37 | -  | -    | -    | -   | -   | -            | -        |

| Clock _                   | 49 | 48 | 47   | 37   | 58  | 55  | 59           | 29       |

#### C. Set-up and Hold Times Relative to Clock (CP) Input.

| CP:                         | <b></b>                     |                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                               |

|-----------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Set-up Time<br>Before H → L | Hold Time<br>After H → L    | Set-up Time<br>Before L → H                                                                                                                                                                                                                                                                                                                                                                                                            | Hold Time<br>After L → H                                                                                                                                                                                                                                                                                      |

| 20                          | 0 (Note 3)                  | 69 (Note 4)                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                             |

| 15                          | Do Not Change               |                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                             |

| _                           | -                           | 51                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                             |

| -                           | -                           | 39                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                             |

| _                           | -                           | 56                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                             |

| -                           | -                           | 55                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                             |

| 11                          | Do Not                      | Change                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                                                                                                                                             |

| -                           | -                           | 16                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                             |

|                             | Set-up Time<br>Before H → L | Set-up Time Before H → L         Hold Time After H → L           20         0 (Note 3)           15         Do Not           -         -           -         -           -         -           -         -           -         -           -         -           -         -           -         -           -         -           -         -           -         -           -         -           -         -           -         - | Set-up Time Before H → L         Hold Time After H → L         Set-up Time Before L → H           20         0 (Note 3)         69 (Note 4)           15         Do Not Change           -         51           -         39           -         56           -         55           11         Do Not Change |

# Timing – Logic

Am2900

#### **TABLE IV E-2**

Guaranteed Combinational Delays  $T_C = -55^{\circ}C$  to  $+125^{\circ}C$ ,  $V_{CC} = 4.5V$  to 5.5V Two's Complement Multiply Instruction  $(I_{8765} = 2_H, I_{4321} = 0_H, I_0 = 0)$

| To Output<br>From Input             | Slice<br>Position | γ   | C <sub>n+4</sub> | G, P | Z (s) | N   | OVR | DB | WRITE | QIO <sub>0</sub><br>QIO <sub>3</sub> | SIOo | SIO <sub>3</sub> | SIO <sub>0</sub> |

|-------------------------------------|-------------------|-----|------------------|------|-------|-----|-----|----|-------|--------------------------------------|------|------------------|------------------|

| A, B Address                        | MSS               | 113 | 93               | -    | -     | 102 | 118 | 52 | -     | _                                    | 97   | -                | _                |

| (Arith, Mode)                       | IS, LSS           | 101 | 93               | 84   | -     | -   | -   | 52 | -     | -                                    | 97   | -                | -                |

| DA, DB Inputs                       | MSS               | 78  | 62               | -    | -     | 66  | 94  | -  | -     | _                                    | 64   | -                | -                |

| DA, DB inputs                       | IS, LSS           | 64  | 62               | 51   | -     | -   | -   | -  | -     | -                                    | 64   | -                | _                |

| EA                                  | MSS               | 85  | 56               | -    | -     | 60  | 87  | _  | -     | _                                    | 58   | -                | _                |

| EA                                  | IS, LSS           | 60  | 56               | 43   | -     | -   | -   | -  | -     | _                                    | 58   | _                | -                |

|                                     | MSS               | 58  | 30               | -    | -     | 40  | 59  | -  | -     | _                                    | 38   | _                | _                |

| C <sub>n</sub>                      | IS, LSS           | 40  | 30               | -    | -     | -   |     | -  | -     | _                                    | 38   | -                | -                |

|                                     | MSS               | 105 | 97               | -    | -     | 89  | 102 | -  | -     |                                      | 71+  |                  | _                |

| l <sub>0</sub>                      | IS                | 105 | 97               | 81   | -     | -   | -   | -  | -     |                                      | 71 - |                  | _                |

|                                     | LSS               | 105 | 97               | 81   | 42    | -   | -   | -  | 53    |                                      | 71+  |                  | -                |

|                                     | MSS               | 112 | 98               | -    | -     | 94  | 111 | -  | -     |                                      | 75+  |                  | _                |

| 4321                                | IS                | 112 | 98               | 85   | -     | -   | -   | -  | -     |                                      | 75+  |                  | _                |

|                                     | LSS               | 112 | 98               | 85   | 43    | -   | -   | -  | 53    |                                      | 75+  |                  | _                |

|                                     | MSS               | 99  | 86               | -    | -     | 78  | 100 | -  | -     |                                      | 74 . |                  | -                |

| 8765                                | IS                | 99  | 86               | 84   | -     | -   | -   | -  | -     |                                      | 74+  |                  | _                |

|                                     | LSS               | 99  | 86               | 84   | 48    | -   | -   | -  | 50    |                                      | 74+  |                  | _                |

| Clock                               | MSS               | 107 | 90               | -    | -     | 89  | 116 | 39 | -     | 42                                   | 91   | -                | _                |

| CIOCK                               | IS, LSS           | 89  | 90               | 74   | 57    | -   | -   | 39 | -     | 42                                   | 91   | -                | -                |

| z                                   | MSS               | 90  | 65               | -    | -     | 70  | 81  | -  | -     | -                                    | 72   | -                | _                |

|                                     | IS                | 90  | 65               | 48   | -     | -   | -   | -  | -     | -                                    | 72   | -                | -                |

| IEN                                 | Any               | -   | -                | -    | -     | -   | -   | -  | 24    | -                                    | -    | _                | _                |

| SIO <sub>3</sub> , SIO <sub>0</sub> | Any               | 26  | _                | -    | -     | _   | -   | _  | -     | _                                    | -    | -                |                  |

$F = S + C_n \text{ if } Z = 0$   $S + R + C_n \text{ is } Z = 1$   $Y_3 = F_3 \oplus \text{OVR (MSS)}$   $Z = Q_0 \text{ (LSS)}$

## Timing – Clocked

Am2900

TABLE IV B Guaranteed Set-up and Hold Times  $T_C = -55^{\circ}C$  to  $+125^{\circ}C$ ,  $V_{CC} = 4.5V$  to 5.5V All Functions

CAUTION: READ NOTES TO TABLE B. NA = Not Applicable; no timing constraint.

|                                     |                       | HIGH-t   | o-LOW  | LOW-to | -HIGH         |                                                  |  |

|-------------------------------------|-----------------------|----------|--------|--------|---------------|--------------------------------------------------|--|

|                                     | With Respect          | <b>1</b> |        | ,      | $\overline{}$ | `                                                |  |

| Input                               | to this Signal        | Set-up   | Hold   | Set-up | Hold          | Comment                                          |  |

| Y                                   | Clock                 | NA       | NA     | 23     | 3             | To store Y in RAM or Q                           |  |

| WE HIGH                             | Clock                 | 25       | Note 2 | Note 2 | 0             | To Prevent Writing                               |  |

| WE LOW                              | Clock                 | NA       | NA     | 35     | 0             | To Write into RAM                                |  |

| A, B as Sources                     | Clock                 | 38       | 3      | NA     | NA            | See Note 3                                       |  |

| B as a Destination                  | Clock and WE both LOW | 6        | Note 4 | Note 4 | 3             | To Write Data only into<br>the Correct B Address |  |

| Q10 <sub>0</sub> , Q10 <sub>3</sub> | Clock                 | NA       | NA     | 23     | 3             | To Shift Q                                       |  |

| 8765                                | Clock                 | 24       | Note 5 | Note 5 | 0             |                                                  |  |

| IEN HIGH                            | Clock                 | 30       | Note 2 | Note 2 | 0             | To Prevent Writing into Q                        |  |

| IEN LOW                             | Clock                 | NA       | NA     | 30     | 0             | To Write into Q                                  |  |

| l <sub>43210</sub>                  | Clock                 | 24       | -      | 74     | 0             | See Note 6                                       |  |

#### Notes:

- For set-up times from all inputs not specified in Table IV B, the set-up time is computed by calculating the delay to stable Y outputs and then allowing the Y set-up time. Even if the RAM is not being loaded, the Y set-up time is necessary to set-up the Q register. All unspecified hold times are less than or equal to zero relative to the clock LOW-to-HIGH edge.

- 2. WE controls writing into the RAM. IEN controls writing into Q and, indirectly, controls WE through the write output. To prevent writing, IEN and WE must be HIGH during the entire clock LOW time. They may go LOW after the clock has gone LOW to cause a write provided the WE LOW and IEN LOW set-up times are met. Having gone LOW, they should not be returned HIGH until after the clock has gone HIGH.

- A and B addresses must be set-up prior to clock LOW transition to capture data in latches at RAM output.

- Writing occurs when CP and WE are both LOW. The B address should be stable during this entire period.

- Because I<sub>8765</sub> control the writing or not writing of data into RAM and Q, they should be stable during the entire clock LOW time unless IEN is HIGH, preventing writing.

- 6. The set-up time prior to the clock LOW-to-HIGH transition occurs in parallel with the set-up time prior to the clock HIGH-to-LOW transition and the clock LOW time. The actual set-up time requirement on I<sub>43210</sub>, relative to the clock LOW-to-HIGH transition, is the longer of (1) the set-up time prior to clock L → H, and (2) the sum of the set-up time prior to clock H → L and the clock LOW time.

## Section

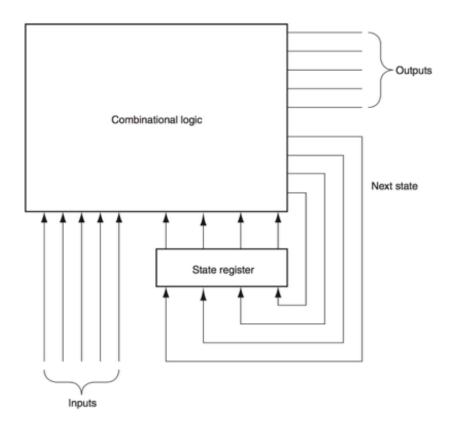

# State Machines FSM

## **State Machines**

FSM

Figure 8.10.3: A finite-state machine is implemented with a state register that holds the current state and a combinational logic block to compute the next state and output functions (COD Figure B.10.3).

The latter two functions are often split apart and implemented with two separate blocks of logic, which may require fewer gates.

#### Section

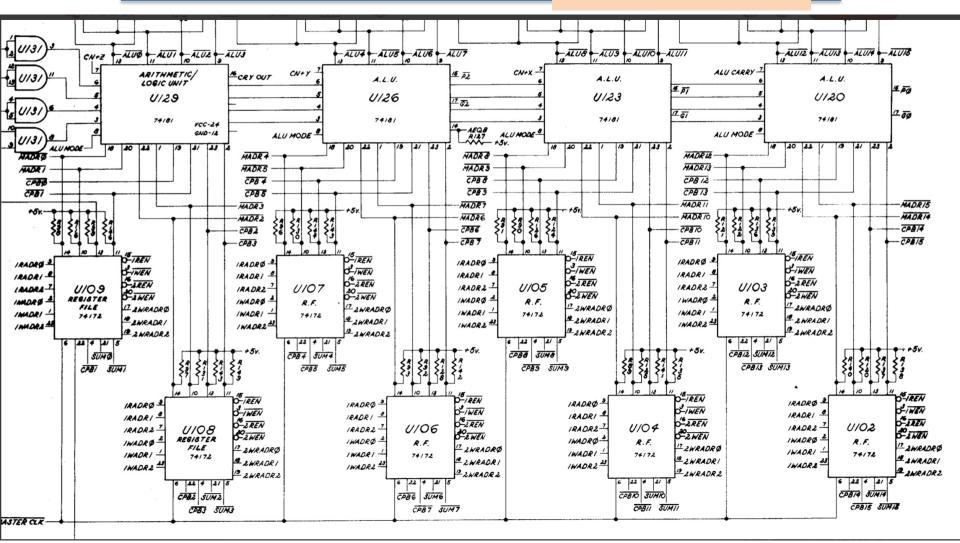

# Computer Logic Boards

## DG Nova 16-bit Mini Circuit

DR JEFF SOFTWARE INDIE APP DEVELOPER © Jeff Drobman 2016-2023

COMP122

4x TI '181 4-bit ALU slice