### **COMP 122**

Rev 8-11-21

# ASSEMBLY Programming/ISA

## MicroControllers

### Dr Jeff Drobman

website drjeffsoftware.com/classroom.html

email <u>jeffrey.drobman@csun.edu</u>

## Index

- **❖**i8051 → slide 9

- ❖PIC18F/32 → slide 18

- **❖**AVR → slide 48

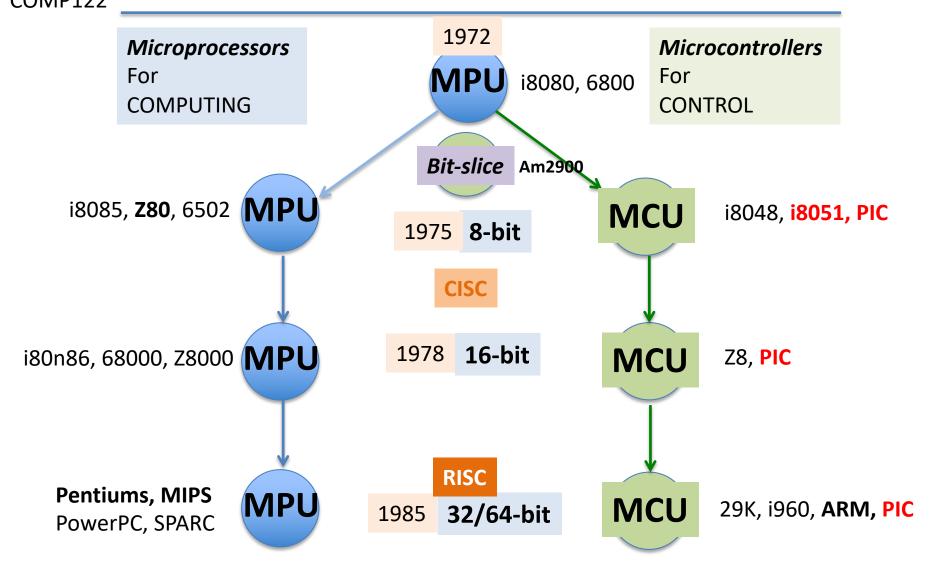

# MPU/MCU Generations

### **Embedded Control**

#### **Microprocessors**

For

**COMPUTING**

- ❖ All 32/64-bit CPUs

- Large data processing applications

- ◆ Employee records

- Accounting

- Payroll

- Operating systems (OS)

- "Apps" (applications)

- ◆ PC/Mac

- Mobile (phones, tablets)

- Web apps

- ◆ Cloud apps (SaaS)

Focus is *Memory* for large Data Files

Large DRAM, Disk, Flash

#### **Microcontrollers**

For

**CONTROL**

- Small embedded control applications (8-bit MCU)

- Appliances

- ◆ Disk controllers

- ◆ Remote controllers

- ◆ Garage/gate openers

- ♦ Tiny

- ♦ Low power

- ♦ Low cost

- Medium embedded control (16-bit MCU)

- User devices (iPods, phones, etc.)

- ◆ Car/Airplane engine control

- Car/Airplane braking & safety

- Car transmission control

- Home Automation (HAN)

- ❖ Large embedded control (32/64-bit MCU)

- ◆ Car/Airplane entertainment

- Car/Airplane navigation, systems management

- Printers (MF)

- Communications gear (WiFi, cable TV boxes)

Focus is **I/O** – Interrupts

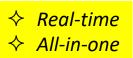

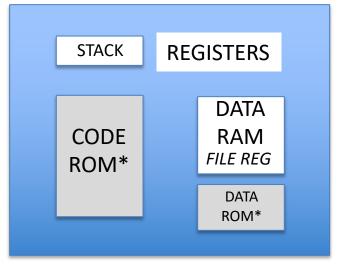

# MCU Block Diagram

8/16/32-bit

#### **BASIC MODEL**

All on one cheap chip

- > No Cache

- No External RAM

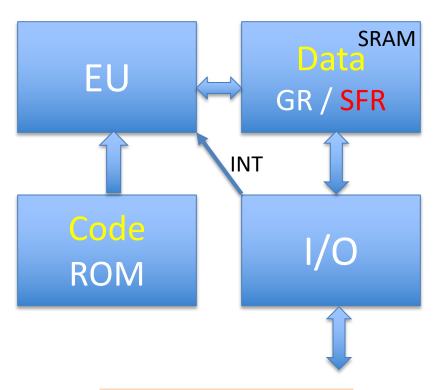

# Memory: CPU vs MCU

#### **MICROPROCESSOR**

MICROCONTROLLER

SMALL INTERNAL MEMORY \*ROM contents must be "programmed" "burned", or masked

**DRAM**

LARGE EXTERNAL MEMORY

### **MCU**

Meanwhile the number of microcontrollers estimated to be shipped in 2019 was estimated at around 27 billion, twelve times as many as the total number of microprocessors. As of 2017, the split was 40% for 32-bit, 33% 8-bit, and 24% 16-bit.

MCU = 12x MPU

So it can be estimated there were somewhere around nine billion 8-bit microcontrollers shipped in 2019. They are predominantly used in embedded systems that have a specific task, such as a small (air fryer, microwave oven) or large (washing machine) appliance; automobile cruise control; intelligent thermostat; etc.

Jeff Drobman Just now

as of 5 years ago (when I last checked), the i8051 was still popular along with the PIC16 and 18 (16-bit). many models sold at <\$1. Atmel's AVR is a popular microcontroller family that is customizable.

# Multiply & Divide

#### **MULTIPLY**

- Unsigned only

- ❖ First convert negative numbers (2sC) NEG op

- Compute result sign: 0 if both signs same, 1 else (not=)

- Complement result if sign is negative NEG op

- Other MPUs use signed multiply (2sC) via "Booth's Algorithm"

#### DIVIDE

- ❖ No hardware, no instruction

- Create subroutine (may find ones in asm library)

- Compute

- Long division

- Non-restoring division

- Iterative subtraction (very slow)

- Use tricks

- Divide by 2 or any 2<sup>n</sup>: right SHIFT by n

- Divide by 10: convert to BCD, then right SHIFT by 4 (reconvert to binary)

- Divide by 5: divide by 10, then multiply by 2 (by shifting after conv. Bin)

# ISA

**i8051**

### Intel 8051

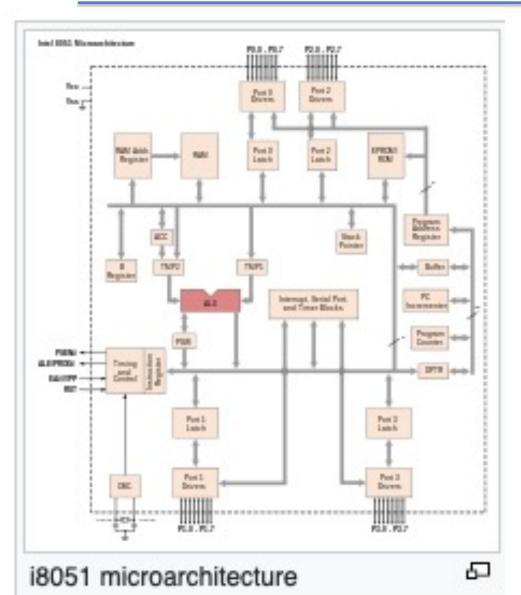

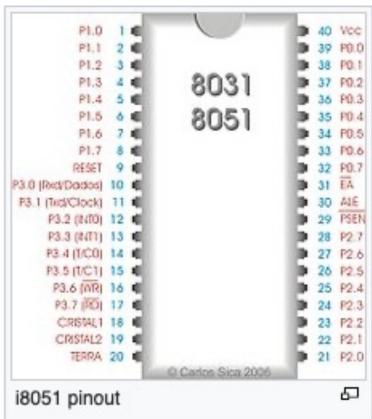

### i8051 MCU

MCS-51

1980

From Wikipedia, the free encyclopedia

The Intel MCS-51 (commonly termed 8051) is a single chip microcontroller (MCU) series developed by Intel in 1980 for use in embedded systems. The architect of the Intel MCS-51 instruction set was John H. Wharton.<sup>[1][2]</sup> Intel's original versions were popular in the 1980s and early 1990s and enhanced binary compatible derivatives remain popular today. It is an example of a complex instruction set computer, and has separate memory spaces for program instructions and data.

Intel's original MCS-51 family was developed using N-type metal-oxide-semiconductor (NMOS) technology like its predecessor Intel MCS-48, but later versions, identified by a letter C in their name (e.g., 80C51) use complementary metal-oxide-semiconductor (CMOS) technology and consume less power than their NMOS predecessors. This made them more suitable for battery-powered devices.

The family was continued in 1996 with the enhanced 8-bit MCS-151 and the 8/16/32-bit MCS-251 family of binary compatible microcontrollers. While Intel no longer manufactures the MCS-51, MCS-151 and MCS-251 family, enhanced binary compatible derivatives made by numerous vendors remain popular today. Some derivatives integrate a digital signal processor (DSP). Beyond these physical devices, several companies also offer MCS-51 derivatives as IP cores for use

in field programmable data array (EDCA) or application appoints integrated circuit (ASIC) decigns

COMP122

COMP122

### Important features and applications [edit]

The 8051 architecture provides many functions (central processing unit (CPU), random access memory (RAM), read-only memory (ROM), input/output (I/O) ports, serial port, interrupt control, timers) in one package:

- 8-bit arithmetic logic unit (ALU) and accumulator, 8-bit registers (one 16-bit register with special move instructions), 8-bit data bus and 2×16-bit address buses, program counter, data pointer, and related 8/11/16-bit operations; hence it is mainly an 8-bit microcontroller

- Boolean processor with 17 instructions, 1-bit accumulator, 32 registers (4 bit-addressable 8-bit) and up to 144 special

1 bit-addressable RAM variables (18 bit-addressable 8-bit)<sup>[4]</sup>

- Multiply, divide and compare instructions

- · Four fast switchable register banks with eight registers each (memory mapped)

- · Fast interrupt with optional register bank switching

- Interrupts and threads with selectable priority<sup>[5]</sup>

- 128 or 256 bytes of on-chip RAM (IRAM)

- Dual 16-bit address bus; it can access 2x2<sup>16</sup> memory locations: 64 KB (65,536 locations) each of ROM (PMEM) and external RAM (XRAM)

- On-chip ROM (not included on 803x variants)

- · Four 8-bit bi-directional input/output ports, bit addressable

- UART (serial port)

- Two 16-bit counter/timers

- Power saving mode (on some derivatives)

#### COMP122

#### Memory architecture [edit]

The MCS-51 has four distinct types of memory: internal RAM, special function registers, program memory, and external data memory.

The 8051 is designed as a modified Von-Neumann Architecture with segregated memory (data and instructions); it can only execute code fetched from program memory, and has no instructions to write to program memory. Which is similar to Harvard Architecture.

Most 8051 systems respect this distinction, and so are unable to download and directly execute new programs. Although the 8051's architecture is unique; the buses to access both types of memory are the same; only the data bus, the address bus, and the control bus leave the processor.

#### Internal RAM [edit]

Internal RAM (IRAM) has an 8-bit address space, using addresses 0 through 0xFF. IRAM from 0x00 to 0x7F can be accessed directly, using an 8-bit absolute address that is part of the instruction. Alternatively, IRAM can be accessed indirectly: the address is loaded into R0 or R1, and the memory is accessed using the @R0 or @R1 syntax.

The original 8051 has only 128 bytes of IRAM. The 8052 added IRAM from 0x80 to 0xFF, which can *only* be accessed indirectly; direct access to this address range goes to the special function registers. Most 8051 clones also have a full 256 bytes of IRAM.

The 32 bytes from 0x00–0x1F memory-map the 8 registers R0–R7. Eight bytes are used at a time; two program status word bits select between four possible banks.

The 16 bytes (128 bits) at IRAM locations 0x20-0x2F are bit-addressable.

#### Special function registers [edit]

Special function registers (SFR) are located in the same address space as IRAM, at addresses 0x80 to 0xFF, and are accessed directly using the same instructions as for the lower half of IRAM. They cannot be accessed indirectly via @R0 or @R1; indirect access to those addresses will access the second half of IRAM.

Sixteen of the SFRs (those whose addresses are multiples of 8) are also bit-addressable.

#### Program memory [edit]

Program memory (PMEM, though less common in usage than IRAM and XRAM) is up to 64 KB of read-only memory, starting at address 0 in a separate address space. It may be on- or off-chip, depending on the particular model of chip being used. Program memory is read-only, though some variants of the 8051 use on-chip flash memory and provide a method of re-programming the memory in-system or in-application.

#### COMP122

#### Registers [edit]

The only register on an 8051 that is not memory-mapped is the 16-bit program counter (PC). This specifies the address of the next instruction to execute. Relative branch instructions supply an 8-bit signed offset which is added to the PC.

Eight general-purpose registers R0–R7 may be accessed with instructions one byte shorter than others. They are mapped to IRAM between 0x00 and 0x1F. Only eight bytes of that range are used at any given time, determined by the two bank select bits in the PSW.

The following is a partial list of the 8051's registers, which are memory-mapped into the special function register space:

#### Stack pointer, SP (0x81)

This is an 8-bit register used by subroutine call and return instructions. The stack grows upward; the SP is incremented before pushing, and decremented after popping a value.

#### Data pointer, DP (0x82-83)

This is a 16-bit register that is used for accessing PMEM and XRAM.

#### Program status word, PSW (0xD0)

This contains important status flags, by bit number:

- 0. Parity, P. Gives the parity (XOR of the bits) of the accumulator, A.

- 1. User defined, UD. May be read and written by software; not otherwise affected by hardware.

- 2. Overflow flag, OV. Set when addition produces a signed overflow.

- 3. Register select 0, RS0. The low-order bit of the register bank. Set when banks at 0x08 or 0x18 are in use.

- 4. Register select 1, RS1. The high-order bit of the register bank. Set when banks at 0x10 or 0x18 are in use.

- 5. Flag 0, F0. May be read and written by software; not otherwise affected by hardware.

- 6. Auxiliary carry, AC. Set when addition produces a carry from bit 3 to bit 4.

- 7. Carry bit, C. Often used as the general register for bit computations, or the "Boolean accumulator".

#### Accumulator, A (0xE0)

This register is used by most instructions.

#### B register (0xF0)

This is used as an extension to the accumulator for multiply and divide instructions.

256 single bits are directly addressable. These are the 16 IRAM locations from 0x20–0x2F, and the 16 special function registers 0x80, 0x88, 0x90, ..., 0xF8. Any bit of these bytes may be directly accessed by a variety of logical operations and conditional branches.

Note that the PSW does not contain the common negative (N), or zero (Z) flags. For the former, the most significant bit of the accumulator can be addressed

COMP122

8051/8052 irregular instructions

| Opcode     | х0                                           | <i>x</i> 1   | x2               | хз                                 | x4                     |  |  |

|------------|----------------------------------------------|--------------|------------------|------------------------------------|------------------------|--|--|

| 0 <i>y</i> | NOP                                          |              | LJMP addr16      | RR A (rotate right)                | INC A                  |  |  |

| 1 <i>y</i> | JBC bit, offset (jump if bit set with clear) |              | LCALL addr16     | RRC A (rotate right through carry) | DEC A                  |  |  |

| 2 <i>y</i> | JB bit, offset (jump if bit set)             |              | RET              | RL A (rotate left)                 | ADD A,#data            |  |  |

| 3 <i>y</i> | JNB bit, offset (jump if bit clear)          |              | RETI             | RLC A (rotate left through carry)  | ADDC A,#data           |  |  |

| 4 <i>y</i> | JC offset (jump if carry set)                |              | ORL address,A    | ORL address,#data                  | ORL A,#data            |  |  |

| 5 <i>y</i> | JNC offset (jump if carry clear)             |              | ANL address,A    | ANL address,#data                  | ANL A,#data            |  |  |

| 6 <i>y</i> | JZ offset (jump if zero)                     | AJMP addr11, | XRL<br>address,A | XRL address,#data                  | XRL A,#data            |  |  |

| 7 <i>y</i> | JNZ offset (jump if non-zero)                | ACALL GUGITI | ORL C,bit        | JMP @A+DPTR                        | MOV A,#data            |  |  |

| 8 <i>y</i> | SJMP offset (short jump)                     |              | ANL C,bit        | MOVC A,@A+PC                       | DIV AB                 |  |  |

| 9 <i>y</i> | MOV DPTR,#data16                             |              | MOV bit,C        | MOVC A,@A+DPTR                     | SUBB A,#data           |  |  |

| Ay         | ORL C,/bit                                   |              | MOV C,bit        | INC DPTR                           | MUL AB                 |  |  |

| Ву         | ANL C,/bit                                   |              | CPL bit          | CPL C                              | CJNE<br>A,#data,offset |  |  |

| Cy         | PUSH address                                 | ress CLR bit |                  | CLR C                              | SWAP A                 |  |  |

| Dy         | POP address                                  |              | SETB bit         | SETB C                             | DA A (decimal adjust)  |  |  |

| Ey         | MOVX A,@DPTR                                 |              | MOVX A,@RØ       | MOVX A,@R1                         | CLR A                  |  |  |

| Fy         | MOVX @DPTR,A                                 |              | MOVX @RØ,A       | MOVX @R1,A                         | CPL A                  |  |  |

COMP122

#### Intel MCS-51 second sources

AMD D87C51 MHS S-80C31 OKI M80C31

Philips PCB80C31 Signetics SCN8031

Temic TS80C32

**COMP122**

#### Derivative vendors [edit]

More than 20 independent manufacturers produce MCS-51 compatible processors. [citation needed]

#### Intel MCS-51 derived microcontrollers

Atmel AT89C2051 Infineon SAB-C515 Philips S87C654

Siemens SAB-C501 STC Micro STC89C52

# ISA

PIC

☐ PIC18F

## **PIC Families**

COMP122

Architecture Back To Top

- Instructions and data on separate busses

- Simultaneous data & instruction bus access

- Wide program memory buses (12, 14 & 16-bit)

- Increased efficiency single cycle instructions

- Available data EEPROM

- Unified toolset for all cores

#### Compare 8-bit PIC® MCU Architectures

|                                       | Baseline Architecture                                | Mid-Range Architecture                                                              | Enhanced Mid-Range Architecture                                                                                          | PIC18 Architecture                                                                                |  |  |

|---------------------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|--|

| Pin Count                             | 6-40 8-64                                            |                                                                                     | 8-64                                                                                                                     | 18-100                                                                                            |  |  |

| Interrupts                            | No Single interrupt capability                       |                                                                                     | Single interrupt capability with hardware context save                                                                   | Multiple interrupt capability with hardware context save                                          |  |  |

| Performance                           | 5 MIPS                                               | 5 MIPS                                                                              | 8 MIPS                                                                                                                   | Up to 16 MIPS                                                                                     |  |  |

| Instructions                          | 33, 12-bit                                           | 35, 14-bit                                                                          | 49, 14-bit                                                                                                               | 83, 16-bit                                                                                        |  |  |

| Program Memory Up to 3 KB Up to 14 KB |                                                      | Up to 14 KB                                                                         | Up to 28 KB                                                                                                              | Up to 128 KB                                                                                      |  |  |

| Data Memory                           | Memory Up to 138 Bytes Up to 368 Bytes               |                                                                                     | Up to 1,5 KB                                                                                                             | Up to 4 KB                                                                                        |  |  |

| Hardware Stack                        | 2 level 8 level                                      |                                                                                     | 16 level                                                                                                                 | 32 level                                                                                          |  |  |

| Features                              | Comparator 8-bit ADC Data Memory Internal Oscillator | In addition to Baseline:  ■ SPI/I²C™  ■ UART  ■ PWMs  ■ LCD  ■ 10-bit ADC  ■ Op Amp | In addition to Mid-Range:  Multiple Communication Peripherals  Linear Programming Space  PWMs with Independent Time Base | In addition to Enhanced Mid-Range:  8x8 Hardware Multiplier  CAN  CTMU  USB  Ethernet  12-bit ADC |  |  |

| Highlights                            | Lowest cost in the smallest form factor              | Optimal cost to performance ratio                                                   | Cost effective with more performance and memory                                                                          | High performance, optimized for C programming, advanced peripherals                               |  |  |

| Total Number of Devices               | 16                                                   | 58                                                                                  | 29                                                                                                                       | 193                                                                                               |  |  |

| Families                              | PIC10, PIC12, PIC16                                  | PIC12, PIC16                                                                        | PIC12FXXX, PIC16F1XX                                                                                                     | PIC18                                                                                             |  |  |

# PIC18F Family

COMP122

Select Product Family: PIC18 Microcontrollers ▼

| Product ▲   | Program<br>Memory<br>KB | RAM<br>Bytes | Pins | Max CPU<br>Speed | Total # of<br>A/D<br>Channels | Max 8 Bit<br>Digital<br>Timers | Max 16<br>Bit Digital<br>Timers | UART | SPI | I2C | Cap.<br>Touch<br>Channels | Segment<br>LCD | Op.<br>Voltage<br>Range (V) |

|-------------|-------------------------|--------------|------|------------------|-------------------------------|--------------------------------|---------------------------------|------|-----|-----|---------------------------|----------------|-----------------------------|

| PIC18F1220  | 4                       | 256          | 18   | 40 MHz           | 7                             | 1                              | 3                               | 1    | 0   | 0   | 0                         | 0              | 2 to 5.5                    |

| PIC18F1230  | 4                       | 256          | 18   | 40 MHz           | 4                             | 0                              | 2                               | 1    | 0   | 0   | 0                         | 0              | 2 to 5.5                    |

| PIC18F1320  | 8                       | 256          | 18   | 40 MHz           | 7                             | 1                              | 3                               | 1    | 0   | 0   | 0                         | 0              | 2 to 5.5                    |

| PIC18F1330  | 8                       | 256          | 18   | 40 MHz           | 4                             | 0                              | 2                               | 1    | 0   | 0   | 0                         | 0              | 2 to 5.5                    |

| PIC18F13K22 | 8                       | 256          | 20   | 64 MHz           | 12                            | 1                              | 3                               | 1    | 1   | 1   | 12                        | 0              | 1.8 to 5.5                  |

| PIC18F13K50 | 8                       | 512          | 20   | 48 MHz           | 9                             | 1                              | 3                               | 1    | 1   | 1   | 9                         | 0              | 1.8 to 5.5                  |

| PIC18F14K22 | 16                      | 512          | 20   | 64 MHz           | 12                            | 1                              | 3                               | 1    | 1   | 1   | 12                        | 0              | 1.8 to 5.5                  |

| PIC18F14K50 | 16                      | 768          | 20   | 48 MHz           | 9                             | 1                              | 3                               | 1    | 1   | 1   | 9                         | 0              | 1.8 to 5.5                  |

| PIC18F2220  | 4                       | 512          | 28   | 40 MHz           | 10                            | 1                              | 3                               | 1    | 1   | 1   | 0                         | 0              | 2 to 5.5                    |

| PIC18F2221  | 4                       | 512          | 28   | 40 MHz           | 10                            | 1                              | 3                               | 1    | 1   | 1   | 0                         | 0              | 2 to 5.5                    |

# PIC18F Products

COMP122

GROUP

#### PIC18 MCU Products

| Product                                                                                                                               | Buy | Status        | Documents | 5K Pricing                                                                                        | Program<br>Memory<br>Size<br>(Kbytes)  | (bytes)                                                  | EEPROM /<br>HEF                                                    | Pin<br>count                 | Max.<br>CPU<br>Speed<br>MHz | Peripheral<br>Pin Select<br>(PPS) | Internal<br>Oscillator                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------|-----|---------------|-----------|---------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------|------------------------------|-----------------------------|-----------------------------------|------------------------------------------------------------------------------------------|

| [Reset] PIC18F1220 PIC18F1230 PIC18F1320 PIC18F1330 PIC18F13K22 PIC18F13K50 PIC18F14K22 PIC18F14K50 PIC18F14K50 PIC18F2220 PIC18F2221 |     |               |           | [Reset]<br>\$1.16<br>\$1.20<br>\$1.23<br>\$1.26<br>\$1.27<br>\$1.30<br>\$1.31<br>\$1.32<br>\$1.32 | [ Reset ] 4 8 16 24 32 48 64 80 96 128 | [ Reset ] 256 512 768 1024 1536 2048 3328 3648 3800 3808 | [ Reset ]<br>0<br>0 / HEF<br>256<br>1024<br>128 / HEF<br>256 / HEF | [Reset] 18 20 28 40 44 64 60 | [Reset] 32 40 42 48 64      | [Reset]<br>No<br>Yes              | [ Reset ]<br>16 MHz<br>16 MHz, 32 kHz<br>32 kHz<br>64MHZ, 64KHz<br>8 MHz, 32 kHz<br>None |

| PIC18F13K22                                                                                                                           | \$  | In Production | 72        | \$1.16                                                                                            | 8                                      | 256                                                      | 256 / HEF                                                          | 20                           | 64                          | No                                | 16 MHz, 32 kHz                                                                           |

| PIC18F24J10                                                                                                                           | \$  | In Production | 72        | \$1.20                                                                                            | 16                                     | 1024                                                     | 0 / HEF                                                            | 28                           | 40                          | No                                | 32 kHz                                                                                   |

| <sup>®</sup> PIC18F23K20                                                                                                              | \$  | In Production | 7         | \$1.23                                                                                            | 8                                      | 512                                                      | 256 / HEF                                                          | 28                           | 64                          | No                                | 16 MHz, 32 kHz                                                                           |

| <sup>®</sup> PIC18F14K22                                                                                                              | \$  | In Production | 72        | \$1.26                                                                                            | 16                                     | 512                                                      | 256 / HEF                                                          | 20                           | 64                          | No                                | 16 MHz, 32 kHz                                                                           |

| PIC18F25J10                                                                                                                           | \$  | In Production | 72        | \$1.27                                                                                            | 32                                     | 1024                                                     | 0 / HEF                                                            | 28                           | 40                          | No                                | 32 kHz                                                                                   |

| <b><sup>®</sup>PIC18F24K20</b>                                                                                                        | \$  | In Production | 72        | \$1.30                                                                                            | 16                                     | 768                                                      | 256 / HEF                                                          | 28                           | 64                          | No                                | 16 MHz, 32 kH                                                                            |

| <b><sup>®</sup>PIC18F23K22</b>                                                                                                        | \$  | In Production | 72        | \$1.31                                                                                            | 8                                      | 512                                                      | 256 / HEF                                                          | 28                           | 64                          | No                                | 16 MHz, 32 kH                                                                            |

| <sup>®</sup> PIC18F13K50                                                                                                              | \$  | In Production | 72        | \$1.32                                                                                            | 8                                      | 512                                                      | 256 / HEF                                                          | 20                           | 48                          | No                                | 16 MHz, 32 kH                                                                            |

| <sup>®</sup> PIC18F25K20                                                                                                              | \$  | In Production | 72        | \$1.37                                                                                            | 32                                     | 1536                                                     | 256 / HEF                                                          | 28                           | 64                          | No                                | 16 MHz, 32 kH                                                                            |

| PIC18F44J10                                                                                                                           |     | In Production | 7         | \$1.44                                                                                            | 16                                     | 1024                                                     | 0/HEF                                                              | 40                           | 40                          | No                                | 32 kHz                                                                                   |

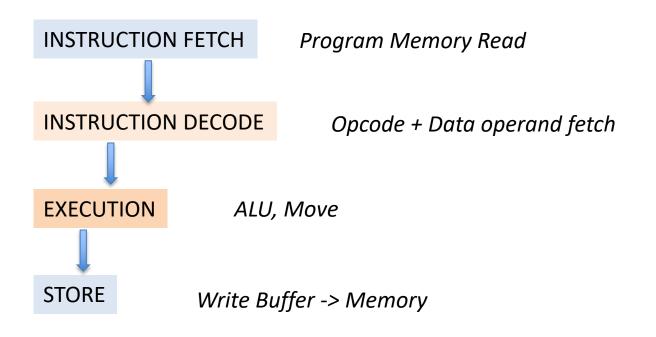

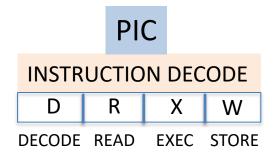

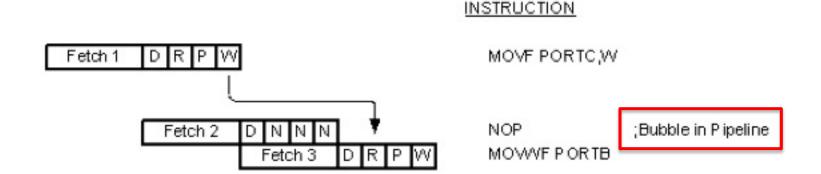

# **Pipelining**

PIC18F

Instruction cycle = 4x clock frequency

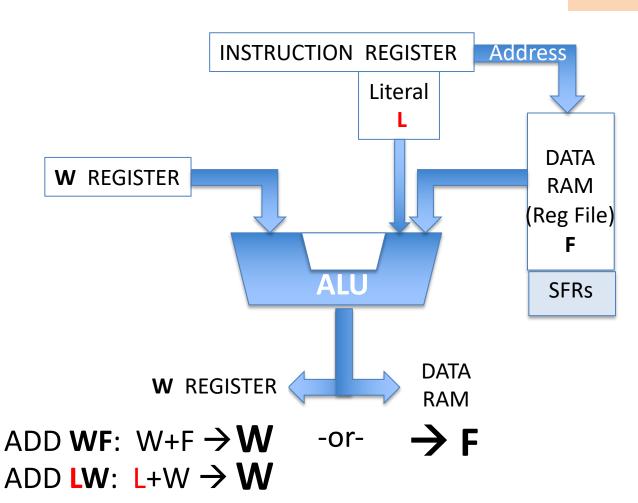

# **ALU Operands**

PIC18F

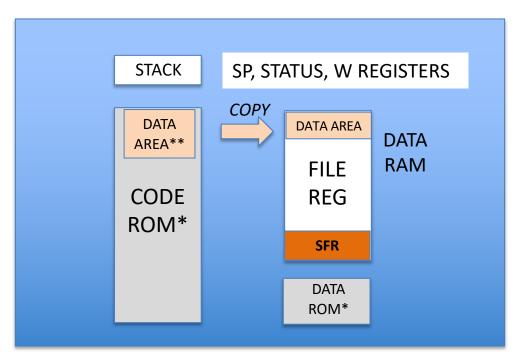

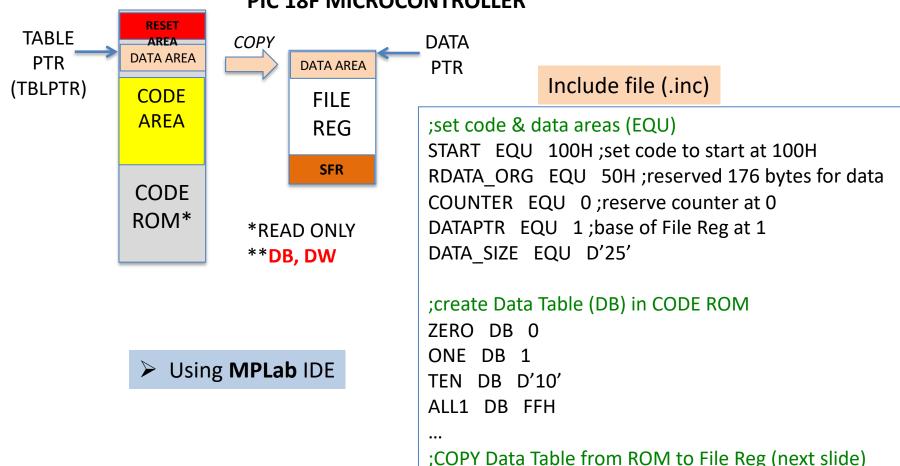

# PIC18F Dual Memory

PIC18F

#### **PIC 18F MICROCONTROLLER**

\*READ ONLY

\*\*use **DB**, **DW**

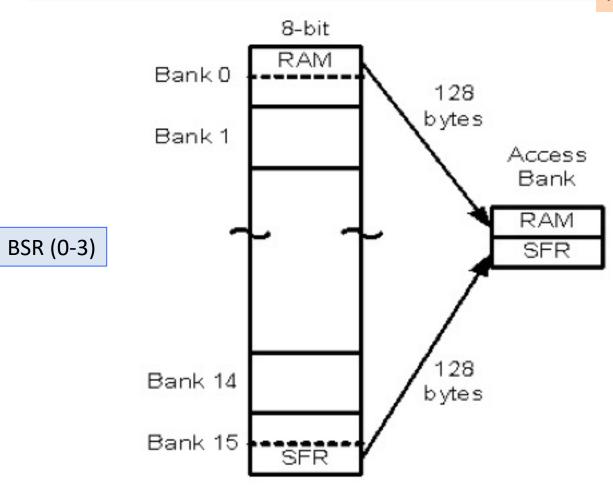

## RAM Banks

PIC18F

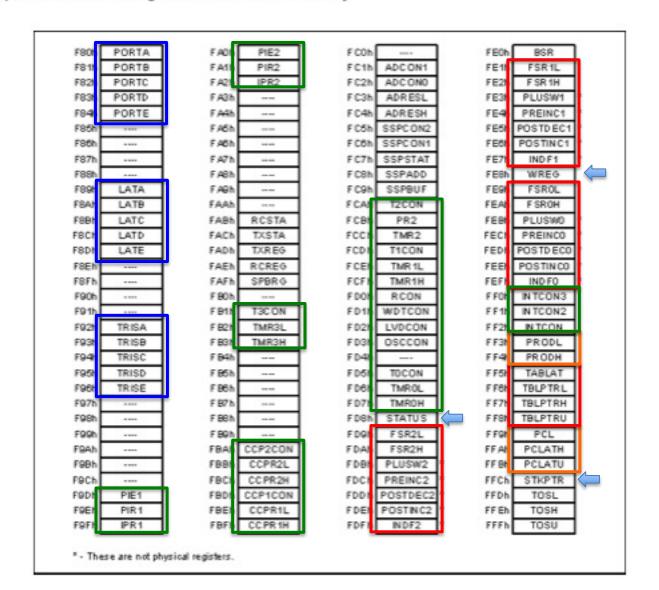

### **SFRs**

COMP122

PIC18F

Figure 2-4. Special Function Registers of the PIC18 Family.

### **ALU & MOVE**

COMP122

PIC18F

ADD

Sets all flags

ADDLW <data>;Add W to Literal <data> → W (only)

ADDWF(C) <addr>, W/F ;Add W to F (Data RAM) → W or F

MOVE

Sets NO flags (1 exception\*)

MOVLW <data> ;Load Literal <data> → W

MOVF\* <addr>, W/F ;Load F at <addr>  $\rightarrow$  W or F (same location; sets N, Z)

**MOVWF** <addr> ;Store  $\mathbf{W} \rightarrow \mathbf{F}$  at <addr>

MOVFF <addr1>,<addr2>;Move F1 → F2 in DataRAM (different location)

**MULTIPLY**

Sets NO flags

**MULLW** ;Multiply W by Literal <data> → PROD [H,L]

MULWF ; Multiply W by F at <addr> → PROD [H,L]

MOV**FF** PRODL, <addr> ;Store PRODL\*  $\rightarrow$  **F** at <addr>

MOVFF PRODH, <addr> ;Store PRODH\*  $\rightarrow$  F at <addr>

\*SFR

# **Addressing Modes**

PIC18F

- Direct (in instruction) MOVF/WF <addr>[8]

- JUMP long-addr [21], BRA offset [+-7]

- ❖ Immediate (Literal Data) MOV/ADDLW k [-128 to +127]

- Indirect (Register indirect, uses FSR)

- LFSR n,<addr> [12-bit] (n=0, 1, 2)

- MOVF/WF INDFn

- CLRF/MOVF POSTINCn/POSTDECn/PREINCn

- ❖ Indexed (Base Register FSR + Index Register W )

- CLRF/MOVF PLUSWn

- INCF <addr>,F ;increment F -or-

- ADDLW 0x01 ;increment W

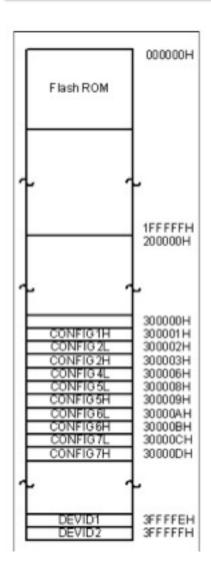

# PIC18F Memory Map

Setup code

#### PIC 18F MICROCONTROLLER

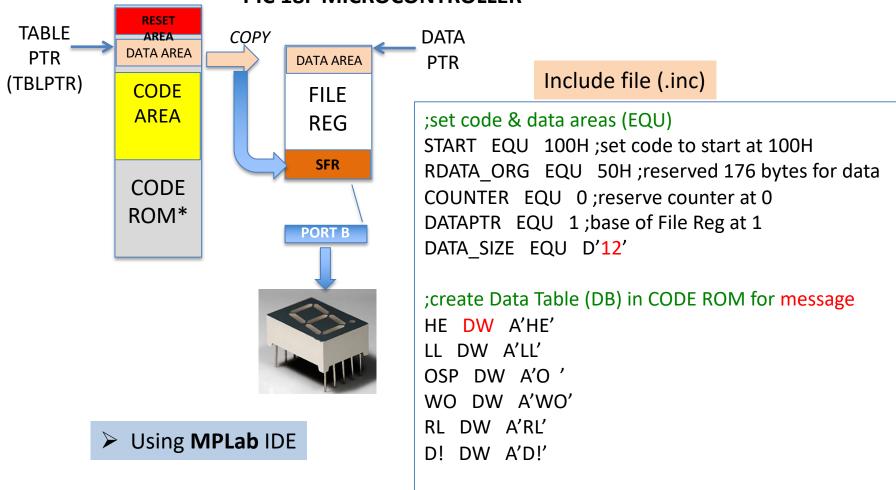

# PIC18F Memory Map

COMP122

"HELLO WORLD"

;COPY Data Table from ROM to PORT B (next slide)

#### PIC 18F MICROCONTROLLER

### Headers

COMP122

PIC18F

;set jump to start (mandatory)

ORG 0

GOTO \_start

; reserve code ROM areas for INTs

ORG 0x08 ;high priority Int

;output Int Ack or GOTO ISR

RETFIE

ORG 0x18 ;low priority Int

;output Int Ack or GOTO ISR

Using MPLab IDE

**RESERVE CODE AREA**

; declare useful constants – 'ORG' opt ZERO EQU 0 ONE EQU 1 TEN EQU D'10' ;not just 10 ALL1 EQU 0xFF START EQU 0x100 ;address 256

**DECLARE CONSTANTS**

ZERO DB 0 ONE DB 1 TEN DB D'10'

ALL1 DB 0xFF

ORG START

\_start NOP

; start your code here

RETFIE

START CODE

## **Use Headers**

PIC18F

➤ Using **MPLab** IDE

# Copy Data Table

PIC18F

```

;Init vars & pointer

MOVLW DATA SIZE

MOVWF COUNTER; init counter

Using MPLab IDE

;LFSR 1,DATAPTR – not needed

;init Table Pointer (21-bit address)

CLRF TBLPTRU ;upper 5 bits

CLRF TBLPTRH; High byte

MOVLW RDATA ORG

MOVWF TBLPTRL; Low byte

;Copy ROM Table into Port B loop

LOOP

TBLRD *+ ;read data from table into TABLAT & inc TBLPTR

MOVFF TABLAT, PORTB

CALR DELAY ; delay loop subroutine

DECF

COUNTER

BNZ

LOOP

```

DO THIS IN THE LAB

# Copy Data Table

**COMP122**

```

8080/8085

6800

; memcpy --

; memcpy --

; Copy a block of memory from one location to another.

Copy a block of memory from one location to another.

Entry parameters

Entry registers

cnt - Number of bytes to copy

BC - Number of bytes to copy

src - Address of source data block

DE - Address of source data block

dst - Address of target data block

HL - Address of target data block

cnt

dw

$0000

Return registers

src

dw

$0000

BC - Zero

$0000

dst

dw

;Origin at 1000h

org

1000h

public

memcpy

public

memcpy

ldab

cnt+1

:Set B = cnt.L

a,b

; Test BC,

loop

mov

; If cnt.L=0, goto check

beg

check

; If BC = 0,

ora

C

loop

ldx

:Set IX = src

src

rz

;Return

ldaa

ix

;Load A from (src)

ldax

d

;Load A from (DE)

;Set src = src+1

inx

;Store A into (HL)

mov

m,a

stx

src

inx

d

; Increment DE

ldx

dst

;Set IX = dst

inx

h

; Increment HL

;Store A to (dst)

staa

ix

dcx

b

:Decrement BC

;Set dst = dst+1

inx

jmp

; Repeat the loop

loop

dst

stx

end

decb

;Decr B

; Repeat the loop

bne

loop

;Set cnt.L = 0

stab

cnt+1

cnt+0

; If cnt. H=0,

check

tst

;Then quit

done

beg

dec

cnt+0

;Decr cnt.H

```

done

decb

bra

rts

loop

;Decr B

;Return

; Repeat the loop

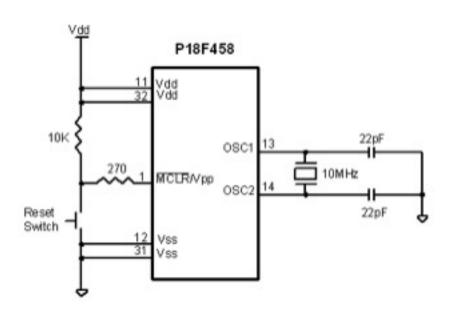

# **Connections Min**

PIC18F

# Configuration

COMP122

|         | PIC18F                                                                                 |  |  |  |  |  |  |  |  |  |

|---------|----------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| U       | 0 U0 R/P-1 U-0 U-0 R/P-1 R/P-1 R/P-1 - OSCSEN — FOSC2 FOSC1 FOSC0                      |  |  |  |  |  |  |  |  |  |

| bit     |                                                                                        |  |  |  |  |  |  |  |  |  |

|         | CONFICAL Parietes for Especialists                                                     |  |  |  |  |  |  |  |  |  |

|         | CONFIG1H Register for Frequency Selection                                              |  |  |  |  |  |  |  |  |  |

| bit 7-6 | Unimplemented: Read as '0'                                                             |  |  |  |  |  |  |  |  |  |

| bit 5   | OSCSEN: Oscillator System Clock Switch Enable bit                                      |  |  |  |  |  |  |  |  |  |

|         | 1 = Oscillator system clock switch option is disabled (main oscillator is source)      |  |  |  |  |  |  |  |  |  |

|         | 0 = Oscillator system clock switch option is enabled (oscillator switching is enabled) |  |  |  |  |  |  |  |  |  |

| bit 4-3 | Unimplemented: Read as '0'                                                             |  |  |  |  |  |  |  |  |  |

| bit 2-0 | FOSC2FOSC 0: Oscillator Selection bits                                                 |  |  |  |  |  |  |  |  |  |

|         | 111 = RC oscillator w/OSC2 configured as RA6                                           |  |  |  |  |  |  |  |  |  |

|         | 110 = HS oscillator with PLL enabled/clock frequency = (4x Fosc)                       |  |  |  |  |  |  |  |  |  |

|         | 101 = EC oscillator w/OSC2 configured as RA6                                           |  |  |  |  |  |  |  |  |  |

|         | 100 = EC oscillator w/OSC2 configured as divide-by-4 clock output                      |  |  |  |  |  |  |  |  |  |

|         | 011 = RC oscillator                                                                    |  |  |  |  |  |  |  |  |  |

|         | 010 = HS oscillator                                                                    |  |  |  |  |  |  |  |  |  |

|         | 001 = XT oscillator                                                                    |  |  |  |  |  |  |  |  |  |

|         | 000 = LP oscillator                                                                    |  |  |  |  |  |  |  |  |  |

| Leger   | with                                                                                   |  |  |  |  |  |  |  |  |  |

|         | eadable bit P = Programmable bit U = Unimplemented bit, read as '0'                    |  |  |  |  |  |  |  |  |  |

|         | /alue when device is unprogrammed u = Unchanged from programmed state                  |  |  |  |  |  |  |  |  |  |

|         | add mail derive to display at the d                                                    |  |  |  |  |  |  |  |  |  |

|         | U-0 U-0 U-0 U-0 R/P-1 R/P-1 R/P-1 R/P-1                                                |  |  |  |  |  |  |  |  |  |

|         | WDTPS2 WDTPS1 WDTPS0 WDTEN                                                             |  |  |  |  |  |  |  |  |  |

|         | bit 7 bt 0                                                                             |  |  |  |  |  |  |  |  |  |

|         | CONFIG2H Configuration Register for Watchdog Times                                     |  |  |  |  |  |  |  |  |  |

| bit 7   |                                                                                        |  |  |  |  |  |  |  |  |  |

| bit 3   |                                                                                        |  |  |  |  |  |  |  |  |  |

|         | 111 = 1:128                                                                            |  |  |  |  |  |  |  |  |  |

|         | 110 = 1:64                                                                             |  |  |  |  |  |  |  |  |  |

|         | 101 = 1:32                                                                             |  |  |  |  |  |  |  |  |  |

|         | 100 = 1:16                                                                             |  |  |  |  |  |  |  |  |  |

|         | 011 = 1:8                                                                              |  |  |  |  |  |  |  |  |  |

|         |                                                                                        |  |  |  |  |  |  |  |  |  |

bit 0 WDTEN: Watchdog Timer Enable bit

1 = WDT enabled

010 = 1:4

001 = 1:2

000 = 1:1

0 = WDT disabled (control is placed on the SWDTEN bit)

Note: The Watchdog Timer postscale select bits configuration used in the PIC18FXXX devices has changed from the configuration used in the PIC18CXXX devices.

# Config Code

**COMP122**

PIC18F

```

#include P18F458.INC

CONFIG OSC = HS, OSCS = OFF

CONFIG WDT = OFF

CONFIG BORV = 45, PWRT = ON, BOR = ON

CONFIG DEBUG = OFF, LVP = OFF, STVR = OFF

ORG 0000H ;start of user code space

;begin user code

;end of user code

END

```

**ASSEMBLY**

```

#pragma config OSC = HS, OSCS = OFF

#pragma config FWRT = OFF, BOR = ON, BORV = 45

#pragma config WDT = OFF LVP = OFF

#pragma config DEBUG = OFF, STVR = OFF

#include <P18F458.h>

void main(void)

{

```

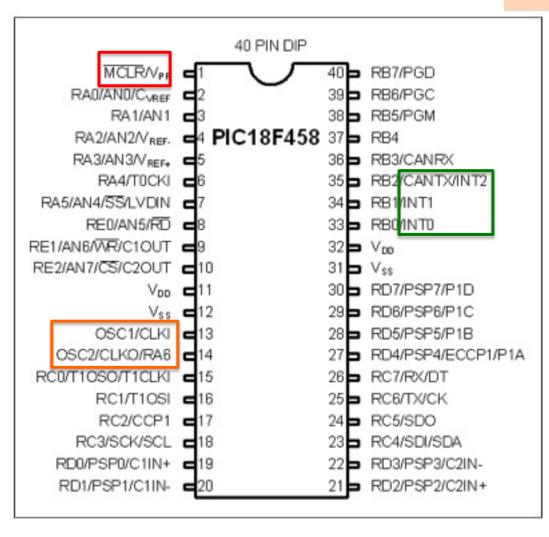

# Interrupts

**COMP122**

PIC18F

**CLASSES**

**PINS**

**ENABLES**

- MASKABLE

- NMI (non)

- INT (maskable)

- INT  $0 \rightarrow Pin 33$

- INT 1  $\rightarrow$  Pin 34

- INT 2  $\rightarrow$  Pin 35

- ❖ GIE global (all 3)

- **❖** INT 0-2

- ❖ PRIE peripherals

**PRIORITIES**

❖ VECTORED

- NVI (non PIC)

❖ HIGH

**❖** LOW

- ❖ PRIORITY (PIC)

- ☐ High

- ☐ Low (High INTs "preempt" Low)

**❖** INTERNAL

- Hardware events

- **Timers**

- ADC

- I/O (S, P)

- Software exceptions

→ SAVED ON STACK

**PROCESSOR STATE**

- ❖ PC

- **❖** ₩

- **STATUS**

- **❖** BSR

# Interrupts/Clocks Pins

PIC18F

### COMP122

# Interrupts C Example

PIC18F

```

#include <p18f4321.h>

void ISR (void); //declares ISR as sub after main

#pragma code Int=0x08

void Intasm()

_asm //use assembly code

GOTO ISR

endasm

#pragma code //org main

Void main()

// do stuff here

While(1) { }

#pragma interrupt ISR

Void ISR (void) //interrupt svc routine

{ //do int stuff

```

# Config Interrupts in C

```

COMP122

```

```

EXTERNAL INTS - PIC18F

Void ISR(); //declare the "ISR" subroutine

SET ORGS

#pragma code int_vectH = 0x08 //assign int "vector" for High Pri Int

Void IntH() {

asm //use assembly code here (no "GOTO" in C)

Or use a "Call":

GOTO ISR

ISR()

endasm

#pragma code int vectL = 0x18 //assign int "vector" for Low Pri Int

#pragma code //main starts here (after the Ints)

Void main ()

PINS

ADCON1=0x0F; //config Port B as input for interrupts

INTCONbits.INTOIE = 1 //enable INTO

INT 0 \rightarrow RB0

INTCON3bits.INT1IE = 1 //enable INT1

SETUP

INT 1 \rightarrow RB1

INTCONbits.INTOF = 0 //clear flag

INT 2 \rightarrow RB2

INTCON3bits.INT1F = 0 //clear flag

INTCON3bits.INT1IP = 0 //set INT1 to Low priority

RCONbits.IPEN = 1 //enable all priority interrupts

INTCONbits.GIEH = 1 //enable Global High priority interrupts

INTCONbits.GIEL = 1 //enable Global Low priority interrupts

While(1); //wait for INTO or INT1

```

### COMP122

## **Timers**

PIC18F

#### **Timers**

- ❖ Timer 0

- ❖ Timer 1

- ❖ Timer 2

- ❖ Timer 3

- Watchdog

#### **PRESCALER**

- Clock pulse counter (a power of 2)

- **2**

- **4**

- **-** 8

- **1**6

- **32**

- **6**4

- **128**

- **256**

### **MODES**

### Timers

- Count UP or DOWN

- Preset start value

- INT on OVERFLOW

- Use INTERNAL clock

### Counters

Use EXTERNAL clock (pin TnCKI)

# Config Timers in C

COMP122

PIC18F

```

#pragma code //main starts here (after the Ints)

Void main ()

SETUP

TOCON=0x06; //config TO

TMR0H = 0XFF //init T0 High byte

TMROL = OXFO //init TO Low byte =-16 (will count UP to 0)

INTCONbits.TMR0IF = 0 //clear Timer0 flag

RUN TIMER

TOCONbits.TMROON = 1 //start timer

While(INTCONbits.TMR0IF ==0); //wait for INT0 or INT1

TOCONbits.TMROON = 0 //stop timer

While(1); //halt

Using Timer0 to create a 1ms delay, assume:

■ 8MHz crystal (=2MHz Instruction rate)

\square Prescale value = 128 (2000/128=16)

```

### **Timers**

- Timer 0

- Timer 1

- ❖ Timer 2

- ❖ Timer 3

- Watchdog

# **Parallel Ports**

D7

PIC18F

| PORTA | PORTB | PORTC | PORTD | PORTE | Port's Bit |

|-------|-------|-------|-------|-------|------------|

| RA0   | RB0   | RC0   | RD0   | RE0   | D0         |

| RA1   | RB1   | RC1   | RD1   | RE1   | D1         |

| RA2   | RB2   | RC2   | RD2   | RE2   | D2         |

| RA3   | RB3   | RC3   | RD3   |       | D3         |

| RA4   | RB4   | RC4   | RD4   |       | D4         |

| RA5   | RB5   | RC5   | RD5   |       | D5         |

| 26    | RB6   | RC6   | RD6   |       | D6         |

Single-Bit Address of a PIC18 Microcontroller

RD7

RC7

RB7

# Write > Read

COMP122

PIC18F

The RAW (Read - After - Write) for two consecutive instructions.

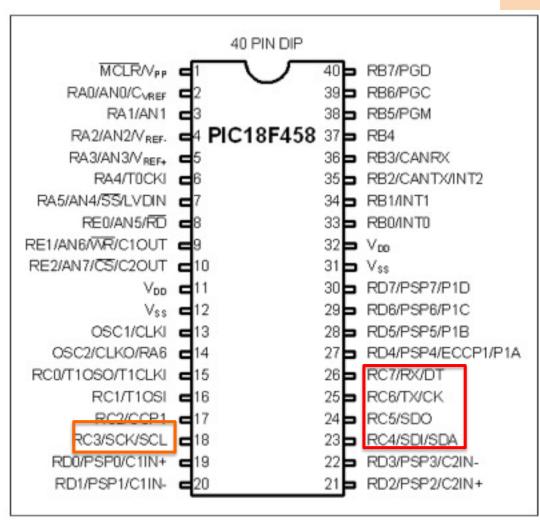

## **Serial Ports**

PIC18F

- ❖ USART async or sync

- ❖ EIA (RS) 232 async

☐ Framed: START, STOP bits

☐ Handshake: RTS, CTS

COVERED

- ❖ SPI sync

- ☐ Clocked data (SCK)

THIS WEEK

- SYNC characters

- Master/slave (clock + data)

- 2 registers

- Tx/Rx shifter

- Buffer

- ❖ I2C sync

- ☐ Peer to peer (IC to IC)

- ❖ SPI − sync (4 pins)

- SDI

- SDO

- SDCLK

- **❖** I2C − sync (4 pins)

- SDI

- SDO

- SDCLK

## Serial Ports — Pins

PIC18F

### COMP122

## PIC32 MCU

### PIC32MX1XX/2XX 28/36/44-PIN

# 32-bit Microcontrollers (up to 256 KB Flash and 64 KB SRAM) with Audio and Graphics Interfaces, USB, and Advanced Analog

#### **Operating Conditions**

- 2.3V to 3.6V, -40°C to +105°C, DC to 40 MHz

- 2.3V to 3.6V, -40°C to +85°C, DC to 50 MHz

### Core: 50 MHz/83 DMIPS MIPS32® M4K®

- MIPS16e<sup>®</sup> mode for up to 40% smaller code size

- · Code-efficient (C and Assembly) architecture

- Single-cycle (MAC) 32x16 and two-cycle 32x32 multiply

#### **Clock Management**

- · 0.9% internal oscillator

- · Programmable PLLs and oscillator clock sources

- Fail-Safe Clock Monitor (FSCM)

- Independent Watchdog Timer

- · Fast wake-up and start-up

#### **Power Management**

- Low-power management modes (Sleep and Idle)

- Integrated Power-on Reset and Brown-out Reset

- 0.5 mA/MHz dynamic current (typical)

- 44 µA IPD current (typical)

#### **Audio Interface Features**

#### **Timers/Output Compare/Input Capture**

- · Five General Purpose Timers:

- Five 16-bit and up to two 32-bit Timers/Counters

- Five Output Compare (OC) modules

- · Five Input Capture (IC) modules

- · Peripheral Pin Select (PPS) to allow function remap

- · Real-Time Clock and Calendar (RTCC) module

#### **Communication Interfaces**

- · USB 2.0-compliant Full-speed OTG controller

- Two UART modules (12.5 Mbps):

- Supports LIN 2.0 protocols and IrDA® support

- Two 4-wire SPI modules (25 Mbps)

- Two I<sup>2</sup>C modules (up to 1 Mbaud) with SMBus support

- · PPS to allow function remap

- · Parallel Master Port (PMP)

#### **Direct Memory Access (DMA)**

- Four channels of hardware DMA with automatic data size detection

- · Two additional channels dedicated for USB

- Programmable Cyclic Redundancy Check (CRC)

## PIC32 MCU

COMP122

#### **Audio Interface Features**

- Data communication: I<sup>2</sup>S, LJ, RJ, and DSP modes

- Control interface: SPI and I<sup>2</sup>C

- Master clock:

- Generation of fractional clock frequencies

- Can be synchronized with USB clock

- Can be tuned in run-time

### **Advanced Analog Features**

- · ADC Module:

- 10-bit 1.1 Msps rate with one S&H

- Up to 10 analog inputs on 28-pin devices and 13 analog inputs on 44-pin devices

- Flexible and independent ADC trigger sources

- Charge Time Measurement Unit (CTMU):

- Supports mTouch™ capacitive touch sensing

- Provides high-resolution time measurement (1 ns)

- On-chip temperature measurement capability

- · Comparators:

- Up to three Analog Comparator modules

- Programmable references with 32 voltage points

Programmable Cyclic Redundancy Check (CRC)

### Input/Output

- 10 mA source/sink on all I/O pins and up to 14 mA on non-standard VOH

- · 5V-tolerant pins

- · Selectable open drain, pull-ups, and pull-downs

- External interrupts on all I/O pins

### **Qualification and Class B Support**

- AEC-Q100 REVG (Grade 2 -40°C to +105°C) planned

- Class B Safety Library, IEC 60730

#### **Debugger Development Support**

- · In-circuit and in-application programming

- 4-wire MIPS<sup>®</sup> Enhanced JTAG interface

- · Unlimited program and six complex data breakpoints

- IEEE 1149.2-compatible (JTAG) boundary scan

# PIC32 MCU

COMP122

#### TABLE 1: PIC32MX1XX 28/36/44-PIN GENERAL PURPOSE FAMILY FEATURES

|                 |      |                                    |                  | Remappable Peripherals |                                        |      |                      |                                    |                    |                     |                  |     |                                          | ls)  |                              |      |          |      |                                 |

|-----------------|------|------------------------------------|------------------|------------------------|----------------------------------------|------|----------------------|------------------------------------|--------------------|---------------------|------------------|-----|------------------------------------------|------|------------------------------|------|----------|------|---------------------------------|

| Device          | Pins | Program Memory (KB) <sup>(1)</sup> | Data Memory (KB) | Remappable Pins        | Timers <sup>(2)</sup> /Capture/Compare | UART | SPI/I <sup>2</sup> S | External Interrupts <sup>(3)</sup> | Analog Comparators | USB On-The-Go (OTG) | l <sup>2</sup> C | PMP | DMA Channels<br>(Programmable/Dedicated) | СТМО | 10-bit 1 Msps ADC (Channels) | RTCC | I/O Pins | JTAG | Packages                        |

| PIC32MX110F016B | 28   | 16+3                               | 4                | 20                     | 5/5/5                                  | 2    | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                      | Y    | 10                           | Υ    | 21       | Υ    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX110F016C | 36   | 16+3                               | 4                | 24                     | 5/5/5                                  | 2    | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                      | Υ    | 12                           | Υ    | 25       | Υ    | VTLA                            |

| PIC32MX110F016D | 44   | 16+3                               | 4                | 32                     | 5/5/5                                  | 2    | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                      | Υ    | 13                           | Υ    | 35       | Υ    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX120F032B | 28   | 32+3                               | 8                | 20                     | 5/5/5                                  | 2    | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                      | Υ    | 10                           | Υ    | 21       | Υ    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX120F032C | 36   | 32+3                               | 8                | 24                     | 5/5/5                                  | 2    | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                      | Υ    | 12                           | Υ    | 25       | Υ    | VTLA                            |

| PIC32MX120F032D | 44   | 32+3                               | 8                | 32                     | 5/5/5                                  | 2    | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                      | Υ    | 13                           | Υ    | 35       | Υ    | VTLA,<br>TQFP,<br>QFN           |

## PIC32 MCU

**COMP122**

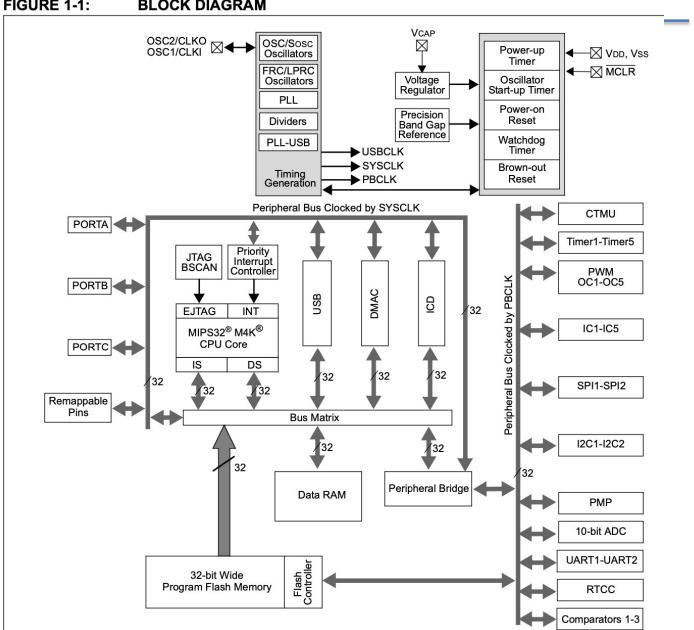

**BLOCK DIAGRAM** FIGURE 1-1:

# ISA

### **AVR** microcontrollers

From Wikipedia, the free encyclopedia

**AVR** is a family of microcontrollers developed since 1996 by Atmel, acquired by Microchip Technology in 2016. These are modified Harvard architecture 8-bit RISC single-chip microcontrollers. AVR was one of the first microcontroller families to use on-chip flash memory for program storage, as opposed to one-time programmable ROM, EPROM, or EEPROM used by other microcontrollers at the time.

AVR microcontrollers find many applications as embedded systems. They are especially common in hobbyist and educational embedded applications, popularized by their inclusion in many of the Arduino line of open hardware development boards.

Various older AVR microcontrollers: ATmega8 in 28-pin narrow dual in-line package (DIP-28N), ATxmega128A1 in 100-pin thin quad flat pack (TQFP-100) package, ATtiny45 in 8-pin small outline (SO-8) package.

### Supported microcontrollers (according to the manual)

| Chip         | Flash size | EEPROM | SRAM | Frequency<br>[MHz] | Package |  |  |

|--------------|------------|--------|------|--------------------|---------|--|--|

| AT90S1200    | 1k         | 64     | 0    | 12                 | PDIP-20 |  |  |

| AT90S2313    | 2k         | 128    | 128  | 10                 | PDIP-20 |  |  |

| AT90S/LS2323 | 2k         | 128    | 128  | 10                 | PDIP-8  |  |  |

| AT90S/LS2343 | 2k         | 128    | 128  | 10                 | PDIP-8  |  |  |

| AT90S4414    | 4k         | 256    | 256  | 8                  | PDIP-40 |  |  |

| AT90S/LS4434 | 4k         | 256    | 256  | 8                  | PDIP-40 |  |  |

| AT90S8515    | 8k         | 512    | 512  | 8                  | PDIP-40 |  |  |

| AT90S/LS8535 | 8k         | 512    | 512  | 8                  | PDIP-40 |  |  |

#### Basic families [edit]

AVRs are generally classified into following:

- tinyAVR the ATtiny series

- Main article: ATtiny microcontroller comparison chart

- 0.5–32 KB program memory

- 6–32-pin package

- · Limited peripheral set

- tinyAVR 0/1/2-series parts, since 2016

- Peripherals equal to or exceed megaAVR 0-series

- Event System

- Improved AVRxt instruction set, hardware multiply

- megaAVR the ATmega series

- 4–256 KB program memory

- 28–100-pin package

- Extended instruction set (multiply instructions and instructions for handling larger program memories)

- Extensive peripheral set'

- megaAVR 0-series parts since 2016

- New peripherals with enhanced functionality

- Event System

- Improved AVRxt instruction set

- AVR Dx focussed on HCl and analog signal conditioning

- 16–128 K program memory

- 24 MHz at 1.8-5.5v

- 14-64-pins

- 4-16 K SRAM, 512b EEPROM

- Part numbers of form AVRffDxpp where ff is flash size, x is family, pp is number of pins

- Example: AVR128DA64 64-pin DA-series with 128k flash

- Async Type D timer can run faster than CPU

- 12-bit ADC, 10-bit DAC

- XMEGA the ATxmega series

- 16–384 KB program memory

- 44–64–100-pin package (A4, A3, A1)

- 32-pin package: XMEGA-E (XMEGA8E5)

- Extended performance features, such as DMA, "Event System", and cryptography support

- Extensive peripheral set with ADCs

#### Internal registers [edit]

The AVRs have 32 single-byte registers and are classified as 8-bit RISC devices.

In the tinyAVR and megaAVR variants of the AVR architecture, the working registers are mapped in as the first 32 memory addresses (0000<sub>16</sub>–001F<sub>16</sub>), followed by 64 I/O registers (0020<sub>16</sub>–005F<sub>16</sub>). In devices with many peripherals, these registers are followed by 160 "extended I/O" registers, only accessible as memory-mapped I/O (0060<sub>16</sub>–00FF<sub>16</sub>).

Actual SRAM starts after these register sections, at address 0060<sub>16</sub> or, in devices with "extended I/O", at 0100<sub>16</sub>.

Even though there are separate addressing schemes and optimized opcodes for accessing the register file and the first 64 I/O registers, all can also be addressed and manipulated as if they were in SRAM.

The very smallest of the tinyAVR variants use a reduced architecture with only 16 registers (r0 through r15 are omitted) which are not addressable as memory locations. I/O memory begins at address 0000<sub>16</sub>, followed by SRAM. In addition, these devices have slight deviations from the standard AVR instruction set. Most notably, the direct load/store instructions

### GPIO ports [edit]

Each GPIO port on a tiny or mega AVR drives up to eight pins and is controlled by three 8-bit registers: DDRx, PORTx and PINx, where x is the port identifier.

- DDRx: Data Direction Register, configures the pins as either inputs or outputs.

- PORTx: Output port register. Sets the output value on pins configured as outputs. Enables or disables the pull-up resistor on pins configured as inputs.

- PINx: Input register, used to read an input signal. On some devices, this register can be used for pin toggling: writing a logic one to a PINx bit toggles the

corresponding bit in PORTx, irrespective of the setting of the DDRx bit.<sup>[10]</sup>

Newer ATtiny AVR's, like ATtiny817 and its siblings, have their port control registers somewhat differently defined. xmegaAVR have additional registers for push/pull, totem-pole and pullup configurations.

#### JTAG [edit]

The Joint Test Action Group (JTAG) feature provides access to on-chip debugging functionality while the chip is running in the target system. [25] JTAG allows accessing internal memory and registers, setting breakpoints on code, and single-stepping execution to observe system behaviour.

Atmel provides a series of JTAG adapters for the AVR:

- 1. The Atmel-ICE<sup>[26]</sup> is the latest adapter. It supports JTAG, debugWire, aWire, SPI, TPI, and PDI interfaces.

- 2. The JTAGICE 3<sup>[27]</sup> is a midrange debugger in the JTAGICE family (JTAGICE mkIII). It supports JTAG, aWire, SPI, and PDI interfaces.

- 3. The JTAGICE mkII<sup>[28]</sup> replaces the JTAGICE and is similarly priced. The JTAGICE mkII interfaces to the PC via USB, and supports both JTAG and the newer debugWIRE interface. Numerous third-party clones of the Atmel JTAGICE mkII device started shipping after Atmel released the communication protocol.<sup>[29]</sup>

- 4. The AVR Dragon<sup>[30]</sup> is a low-cost (approximately \$50) substitute for the JTAGICE mkII for certain target parts. The AVR Dragon provides in-system serial programming, high-voltage serial programming and parallel programming, as well as JTAG or debugWIRE emulation for parts with 32 KB of program memory or less. ATMEL changed the debugging feature of AVR Dragon with the latest firmware of AVR Studio 4 AVR Studio 5 and now it supports devices over 32 KB of program memory.

- 5. The JTAGICE adapter interfaces to the PC via a standard serial port. [31] Although the JTAGICE adapter has been declared "end-of-life" by Atmel, it is still supported in AVR Studio and other tools.

JTAG can also be used to perform a boundary scan test, [32] which tests the electrical connections between AVRs and other boundary scan capable chips in a system. Boundary scan is well-suited for a production line, while the hobbyist is probably better off testing with a multimeter or oscilloscope.